# Mesoscopic Phenomena in Nanometer Scale MOS Devices

#### von der

Fakultät für Elektrotechnik der

#### Universität Dortmund

genehmigte Dissertation

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften

von

Gilson Inácio Wirth

Dortmund 1999

Tag der mündlichen Prüfung: 4. August 1999

Hauptreferent: Prof.Dr.-Ing. K. Goser Korreferent: Prof.Dr.rer.nat. W. R. Fahrner

| 1 | Intr                          | oduction                                                | 9  |  |  |  |  |  |

|---|-------------------------------|---------------------------------------------------------|----|--|--|--|--|--|

| 2 | The                           | MOSFET                                                  | 13 |  |  |  |  |  |

|   | 2.1                           | Principles of Operation                                 | 13 |  |  |  |  |  |

|   |                               | 2.1.1 The Inversion Layer                               | 14 |  |  |  |  |  |

|   |                               | 2.1.2 Current-Voltage Characteristics                   | 16 |  |  |  |  |  |

|   | 2.2                           |                                                         | 19 |  |  |  |  |  |

|   | 2.3                           | Channel Carrier Quantization                            | 21 |  |  |  |  |  |

|   | 2.4                           |                                                         | 27 |  |  |  |  |  |

| 3 | Sam                           | ples and Experimental Setup                             | 29 |  |  |  |  |  |

|   | 3.1                           | Sample Layout and Parameters                            | 29 |  |  |  |  |  |

|   | 3.2                           | Experimental Setup for Measurements at Low Temperature  | 33 |  |  |  |  |  |

|   | 3.3                           | Experimental Setup for Measurements at Room Temperature | 37 |  |  |  |  |  |

| 4 | Peri                          | Periodic Oscillations: Experimental Results             |    |  |  |  |  |  |

|   | 4.1                           | $I_D \times V_G$ Characteristics                        | 39 |  |  |  |  |  |

|   | 4.2                           | $I_D \times V_D$ Characteristics                        | 44 |  |  |  |  |  |

|   | 4.3                           | Source Voltage Sweep                                    | 48 |  |  |  |  |  |

|   | 4.4                           | Magnetic Field Dependence                               | 49 |  |  |  |  |  |

| 5 | Peri                          | odic Oscillations: Theory                               | 53 |  |  |  |  |  |

|   | 5.1                           | Hopping Conductance and Resonant Tunneling              | 53 |  |  |  |  |  |

|   | 5.2                           | Weak Interference between Source and Drain              | 57 |  |  |  |  |  |

|   | 5.3                           | The Quantum Transport Model proposed by Dorda           | 58 |  |  |  |  |  |

|   | 5.4                           | Charge Density Waves                                    | 60 |  |  |  |  |  |

|   | 5.5                           | Coulomb Blockade in a Single Dot                        | 61 |  |  |  |  |  |

|   | 5.6                           | Coulomb Blockade in Parallel Dots                       | 72 |  |  |  |  |  |

| 6 | The Random Telegraph Signal 7 |                                                         |    |  |  |  |  |  |

|   | 6.1                           | Single-Electron Switching                               | 77 |  |  |  |  |  |

|   |                               | 6.1.1 Capture and Emission Kinetics                     | 77 |  |  |  |  |  |

|   |                               | 6.1.2 The Amplitude of RTS                              | 81 |  |  |  |  |  |

|   | 6.2                           | Discussion                                              | 83 |  |  |  |  |  |

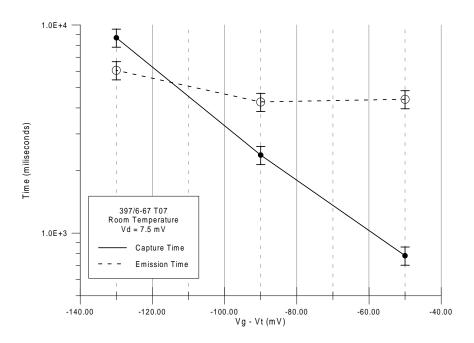

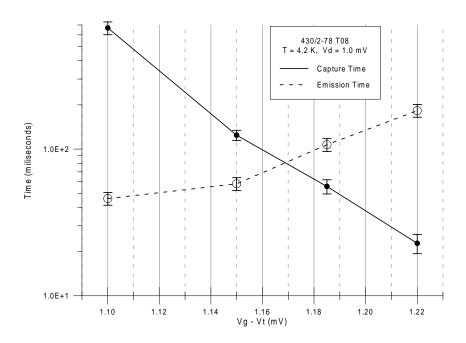

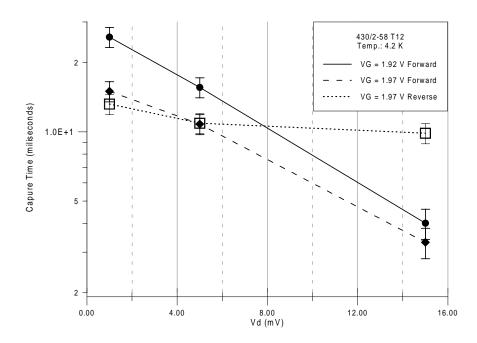

|    | 6.2.1       | Capture and Emission Times as a Function of Bias Point | . 84 |

|----|-------------|--------------------------------------------------------|------|

|    | 6.2.2       | Amplitude as a Function of Bias Point                  | . 90 |

| 7  | Relevance f | or Nanoscale Electronics                               | 97   |

| 8  | Conclusion  |                                                        | 101  |

| A  | Kurzfassun  | g                                                      | 103  |

| Bi | bliography  |                                                        | 106  |

# List of Symbols

B Magnetic field

c Speed of light in vacuum

$C_{ox}$  Oxide capacitance per unit area

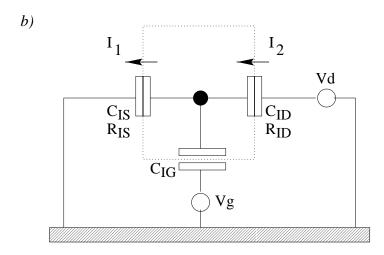

$C_{ID}$  Capacitive coupling between island and drain Capacitive coupling between island and gate Capacitive coupling between island and source

$C_{IS}$  Total island capacitance

*e* Magnitude of the electron charge

$E_B$  Energy barrier

$E_C$  Conduction band edge  $E_{ch}$  Charging energy  $E_F$  Fermi level

$E_{Fi}$  Intrinsic Fermi level  $E_T$  Trap energy level  $E_V$  Valence band edge FET Field Effect Transistor P Planck's constant

h Planck's constant divided by  $2\pi$   $g_m$  Drain conductance of a transistor Transconductance of a transistor

$I_B$  Bulk current  $I_D$  Drain current  $I_G$  Gate current  $I_S$  Source current  $k_B$  Boltzmann constant l Mean free path L Channel length

$L_{design}$  Design channel length  $L_{eff}$  Effective channel length MBE Molecular Beam Epitaxy MOS Metal-oxide-semiconductor

MOSFET Metal-oxide-semiconductor field effect transistor

$m_e$  Free electron mass

$m_*$  Charge carrier effective mass

$m_e^*$  Electron effective mass  $m_h^*$  Hole effective mass

*n* Electron concentration in the conduction band

$n_i$  Intrinsic electron concentration in the conduction band

*NDR* Negative differental resistance

$N_a$  Acceptor density  $N_d$  Donor density

$N_e$  Density of states of electrons in the conduction band

$N_a$  Acceptor density

$N_{inv}$  Inversion layer charge density

$N_{trap}$  Trapped charge density

p Hole concentration in the valence band

$p_i$  Intrinsic hole concentration in the valence band

RTS Random telegraph signal SOI Silicon-on-insulator

*T* Temperature

$T_e$  Electron temperature  $T_l$  Lattice temperature  $t_{ox}$  Gate oxide thickness v Velocity of the electron

$\overline{v}$  Mean velocity of the electrons  $v_s$  Saturation velocity of the electron  $v_{th}$  Thermal velocity of the electron

Bulk voltage  $V_{B}$ Drain voltage  $V_D$  $V_{FB}$ Flat-band voltage  $V_G$ Gate Voltage  $V_{GB}$ Gate to bulk bias  $V_{GS}$ Gate to source bias  $V_I$ Voltage at the island Source voltage  $V_{\mathcal{S}}$ Threshold voltage  $V_T$ WChannel width

$\varepsilon_0$  Free space permittivity

$\varepsilon_{sc}$  Static dielectric constant of the semiconductor

$\varepsilon_{ox}$  Static dielectric constant of the oxide

$\phi_S$  Surface potential  $\phi_B$  Bulk potential

| $\vec{k}$   | Wave vector                                     |

|-------------|-------------------------------------------------|

| $k_{x}$     | Component of the wave vector in the x-direction |

| $k_{y}$     | Component of the wave vector in the y-direction |

| $k_z$       | Component of the wave vector in the z-direction |

| λ           | Wave length                                     |

| $\lambda_F$ | Fermi wave length                               |

| $\mu$       | Charge carrier mobility                         |

| $\mu_n$     | Electron mobility                               |

| $\mu_p$     | Hole mobility                                   |

| $\omega_c$  | Cyclotron frequency                             |

| $ec{p}$     | Momentum of a particle                          |

| Ψ           | Electron wavefunction                           |

| $	au_c$     | Mean electron capture time                      |

| $\tau_e$    | Mean electron emission time                     |

## 1. Introduction

The key point in the success of the semiconductor industry is its ability to continuously provide electronic products with decreasing cost per function as well as, at the same time, increasing performance. This is a result of a steady reduction in the feature size combined with a steady rise in density. In this framework, MOSFETs are being aggressively scaled down to dimensions well below 100 nm. However, at a given device dimension, the scaling of the physical processes breaks down and new phenomena that are absent in larger structures can dominate device behavior. The SIA roadmap (SIA - Semiconductor Industry Association 1997) predicts a minimum feature size of 35 nm and  $10^8$  transistors per  $cm^2$  for the commercial CMOS technology around 2012. It is now quite obvious that the behavior of the devices that will build up the circuits produced with this technology will significantly deviate from the behavior of their counterparts of greater dimensions. This means that the modeling and characterization community has to quickly respond to the challenges related to the further shrinking of device size. Subsequently, if devices are not properly characterized and modeled, this can turn out to be a barrier for further development in the semiconductor industry. The main scope of this work is to help and speed up the proper characterization and modeling of sub-100 nm MOSFETs.

The main purpose of modeling and characterization is to make possible the quantitative investigations needed for optimization and diagnosis, but it is also important to provide insight into technology directions and potentials. Even if the requirements for the commercial application of a particular technology node are not met, modeling and characterization is still a very useful activities since it provides many important technical insights.

Characterization and modeling are known to consist of three steps that are intimately related:

- 1. Elaboration of Models: Models are mental abstractions of reality, created with the help of mathematical tools.

- 2. Simulation: Taking advantage of modern computational facilities, models can be implemented in computer codes, which can then be used to predict the behavior of objects under study in an efficient way.

- 3. Calibration and Validation: The results obtained in the simulation step are compared to representative experimental data to validate the model and to obtain adequate numerical values for parameters.

These three activities compose a cycle that can be interactively repeated until a suitable model is achieved

10 Introduction

In the scope of the work presented in the next chapters, electrical measurements were carried out on samples processed at the facilities available at the *Lehrstuhl für Baulemente der Elektrotechnik*. The measured data represents the reality to be modeled. This work deals with physical models. Physical models intend to represent mathematically the understanding of the physical properties of the devices being studied.

In the subsequent steps, the experimental data obtained is compared to the predictions of available models, some of them implemented in simulators. Numerical values for parameters are obtained and the adequacy of the model is checked. If the model shows deficiencies, a new approach to overcome the deficiencies is proposed. Eventually the cycle is repeated, with new measurements and simulations being performed. This is the methodology used in this work.

The term mesoscopic phenomena, the main subject of this work, has been introduced to describe the characteristics of systems that are neither microscopic (one or few atoms) nor macroscopic. Meso is borrowed from the Greek, meaning middle. In such systems the wave nature of electron transport or the discrete charge nature of electrons may become relevant.

Before the main results obtained are reported, the basic theory needed to follow the discussions undertaken is reviewed in chapter 2. A brief description of the particular technology used to process the devices studied is also presented in this chapter. In the next chapter, sample preparation and the experimental setup used for electrical characterization are described.

In chapter 4 experimental results showing mesoscopic phenomena in the electrical behavior of sub-100 nm MOSFETs at low temperature are presented.

Unexpected periodic oscillations with negative differential resistance (NDR) are present in the  $I_D \times V_G$  characteristics. The oscillations, present from sub-threshold up to strong inversion, are reproducible from sample to sample and with temperature cycling. Investigations are undertaken to verify if there is a relation between device geometry an oscillation pattern. Measurements are carried out at temperatures between 300 mK and 35 K, and magnetic fields up to 15 T are applied.

This is the first time that such phenomena are reported for a conventional bulk MOS system, suggesting that the electrical behavior of ultra short channel devices may still be an open question.

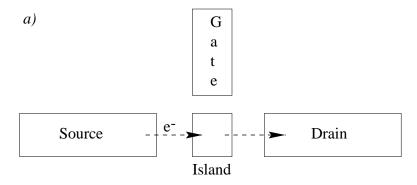

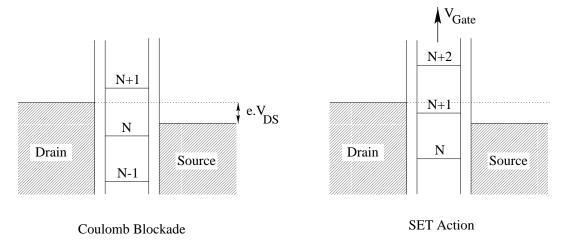

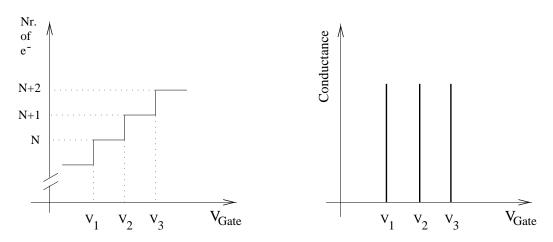

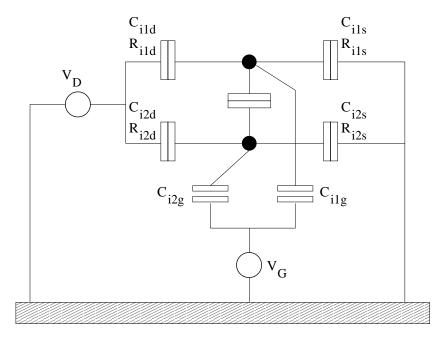

In chapter 5 various electric transport models for small size MOS systems are studied. For several reasons, Coulomb blockade seems to be a rather plausible explanation for the mesoscopic phenomena presented in chapter 4, although some questions, discussed in sections 5.5 and 5.6, remain open.

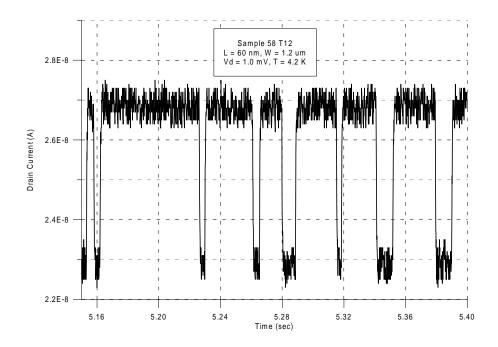

In chapter 6 another single electron switching phenomena is discussed. Namely, the possibility of studying the behavior of individual defect sites in the oxide is demonstrated. The capture and emission of charge carriers from a single defect site brings up discrete changes in the drain current. This is known as the random telegraph signal (RTS). Studying the bias-voltage dependence of the RTS it is possible to determine the geometrical and energetical location of these defects. It is shown that a trap can be used as a probe into the local surface potential. It is also shown that the behavior of the RTS does depend on the properties of the channel electrons close to the defect state, making RTS analysis a valuable way to study effects as Coulomb scattering, electron gas heating and the mechanisms of relevance for electrical channel formation in very small area devices.

If the active device area is decreased, the relative importance of the channel region affected by the defect increases. The study of the random telegraph signal in very small area devices is thus of significance. Noise in general, and the RTS noise in particular, may become an issue for advanced circuitry. The steady lowering of the supply voltages combined with the decrease in device active area will make systems more sensitive to fluctuations in device characteristics.

The investigations carried out in this work intend to contribute to the better understanding of the properties of ultra short MOS devices, a necessary issue to produce optimized and reliable systems, leading ultimately to better products.

12 Introduction

This chapter starts with a brief review of the operation principles of the Metal Oxide Semiconductor Field Effect Transistor (MOSFET), followed by a description of the temperature dependence of the parameters relevant to this work. After that the effects of the quantization of the transverse electron motion in the inversion layer are discussed.

The last section of this chapter describes briefly the particular technology used to process the devices at nanoscale.

#### 2.1 Principles of Operation

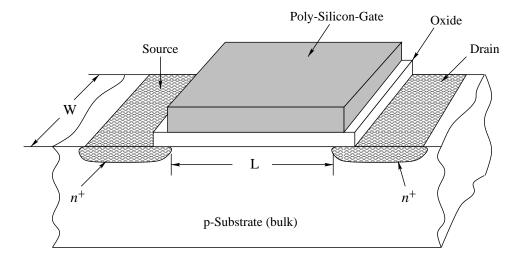

The MOSFET is a four terminal device, as shown in Fig. 2.1. The gate and the bulk terminals define a capacitor where the gate is insulated from Si by a dielectrica, such as  $SiO_2$ . The region beneath the gate oxide and between source and drain is called the channel. First, it will be assumed that bulk, drain and source are at the same potential. Depending on whether  $V_G$ , the voltage between gate and the other terminals, is equal to, less than, or greater than the flatband voltage  $V_{FB}$ , the channel can be in the flat-band condition, in accumulation, in depletion or inversion. The flat-band voltage is the external voltage used between the gate and the bulk terminals to keep the channel neutral by canceling the effects of the contact potentials and the "parasitic" charge that exists within the oxide as well as at the oxide-semiconductor interface.

For the NMOS device of Fig. 2.1, if a voltage less than the flat-band voltage is applied between gate and bulk a positive charge is induced at the oxide-semiconductor interface. As the bulk is p-type, accumulation of excess holes occur at the interface.

If  $V_G$  increases above  $V_{FB}$  the positive charge on the gate will induce a negative charge in the channel. If  $V_G$  is not much higher than  $V_{FB}$ , the positive potential at the surface with respect to the bulk will simply drive holes away from the surface, leaving it depleted from mobile carriers. This condition is called depletion. The charge in the channel consists of ionized acceptor atoms.

If  $V_G$  increases further, more acceptor atoms are uncovered and the potential in the channel becomes sufficiently positive to attract a significant number of free electrons to the surface. Eventually, with a sufficiently high  $V_G$ , the density of electrons will exceed that of holes at the surface. Now one has the so called inversion layer.

The inversion layer is contacted electrically at the two ends by the source and the drain. By applying a voltage between these ends, a current can be caused to flow in the layer. Since the number of carriers available for conduction depends on the gate potential, the latter can be used to create or eliminate the inversion layer as well as to modulate its conduction.

**Figure 2.1:** Simplified structure of a *n*-channel MOS transistor.

#### 2.1.1 The Inversion Layer

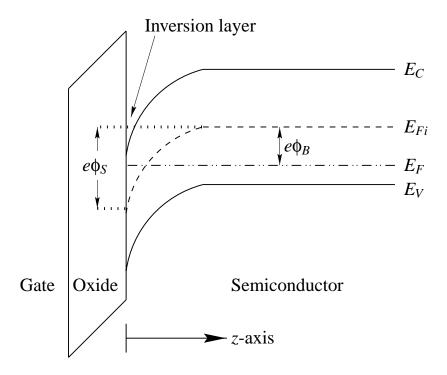

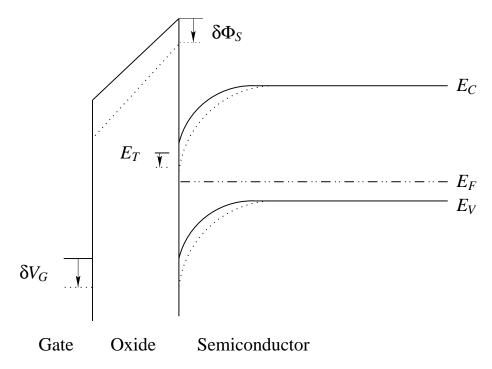

Due to the importance of the inversion layer in this work, it will be now examined in quantitative detail. In Fig. 2.2 the bandbending of the semiconductor in the channel region is shown. The bandbending is described by the quantity  $e\phi(z)$ , which measures the position of the intrinsic Fermi level with respect to the bulk intrinsic Fermi level, and its value at the oxide-semiconductor interface (where z=0) is  $e\phi_S$ , as shown in Fig. 2.2. The z-axis is assumed perpendicular to the oxide-semiconductor interface, increasing in the direction into the semiconductor. Let  $E_{Fi}(z)$  be the intrinsic Fermi level, i.e. the Fermi level in an undoped semiconductor, and  $e\phi_B$  be the difference between the intrinsic Fermi level and the Fermi level in the bulk. Now a quantitative definition of the Flat-Band, Accumulation, Depletion and Inversion conditions qualitatively described above is possible:

•  $\phi_S < 0$ : Accumulation.

•  $\phi_S = 0$ : Flat-band.

•  $0 < \phi_S < \phi_B$ : Depletion.

•  $\phi_S > \phi_B$ : Weak inversion.

•  $\phi_S > 2\phi_B$ : Strong inversion.

Because of bandbending, the electron distribution in the channel depends upon the position z and upon the gate voltage. In the bulk region the gate potential does not affect the electron concentration. This electron concentration, called  $n_0$ , is (Singh 1994)

$$n_0 = n_i exp\left(\frac{-e\phi_B}{k_B T}\right) \tag{2.1}$$

**Figure 2.2:** The bandbending in the p-semiconductor due to a positive gate bias  $V_G$ , leading to an inversion layer.

where  $n_i$  is the intrinsic carrier concentration, T the temperature and  $k_B$  the Boltzmann constant.

Using Boltzmann statistics, the position dependent electron concentration in the inversionlayer can be calculated as being

$$n(z) = n_0 exp\left(\frac{e\phi(z)}{k_B T}\right)$$

(2.2)

The hole concentration is similarly given by

$$p(z) = p_0 exp\left(\frac{-e\phi(z)}{k_B T}\right)$$

(2.3)

where  $p_0$  is the equilibrium hole concentration in the bulk, that can be calculated similarly as  $n_0$  in eq. 2.1.

Solving the Poisson equation using these charge-potential relations one can relate the charge to the externally applied potential. It comes out that once the strong inversion condition is satisfied, the depletion width does not change because the free carriers induced after inversion start preventing further depletion. In fact, because of the large density of states in the conduction

band, once strong inversion is achieved the surface potential  $\phi_S$  gets virtually pinned to the value  $2\phi_B$ . The width of the depletion region at this point is given by

$$W_{max} = \sqrt{\frac{4\varepsilon_{sc}\phi_B}{eN_a}} \tag{2.4}$$

where  $\varepsilon_{sc}$  is the permittivity of the semiconductor and  $N_a$  is the channel doping. The corresponding value of  $V_G$  (at the point where strong inversion is reached) is called the threshold voltage (Singh 1994)

$$V_T = V_G(\phi_S = 2\phi_B) = V_{FB} + 2\phi_B + \frac{\sqrt{4e\varepsilon_{sc}N_a\phi_B}}{C_{ox}}$$

(2.5)

For  $V_G > V_T$ , the charge in the channel consists of the free carriers in the inversion layer and the fixed charge of the dopants in the depletion region. For this bias the depletion layer charge is constant, and a small change  $\delta V_G$  in the gate potential will induce a change  $\delta Q_{inv}$  in the inversion layer charge given by

$$\delta Q_{inv} = \delta V_G \frac{\varepsilon_{ox}}{t_{ox}} = \delta V_G \cdot C_{ox}$$

(2.6)

where  $t_{ox}$  is the gate oxide thickness.

#### 2.1.2 Current-Voltage Characteristics

Now a quantitative analysis of what happens if a potential is applied at the drain contact of a MOSFET is given. It will be assumed that source and bulk are at the same potential, as it is usually the case in practical applications.

The first step is to establish the relation between the channel charge at any point x along the channel and the gate and drain potentials. As the inversion layer is contacted at the drain side its potential will no longer be pinned at  $2\phi_B$ . The extension of the depletion layer is then not limited to the value implied by 2.4. Assuming that both ends of the channel are in strong inversion, the surface potential, now a function of x, the direction along the channel, can be written as

$$\Phi_S(x) = 2\Phi_B + V_C(x) \tag{2.7}$$

where  $V_c(x)$  is the x-dependent channel potential, assumed to zero at the source and equal to  $V_D$  at the drain.

Solving the Poissons equation again, using the charge-potential relations given by 2.2 and 2.3, the position dependent inversion layer charge in the channel comes out to be (Singh 1994)

$$Q_{dep}(x) = -\sqrt{2\varepsilon_{sc}eN_a[V_c(x) + 2\phi_B]}$$

(2.8)

As long as both ends of the channel are in strong inversion the current  $I_D$  between drain and source is mainly due to carrier drift. Making the usual constant mobility  $\mu_n$  approximation it will be given by

$$I_D = -Q_{inv}\mu_n W \frac{\partial V_c(x)}{\partial x}$$

(2.9)

where W is the channel width.

The position dependent charge in the inversion layer can be calculated subtracting the depletion layer charge from the total charge in the channel

$$Q_{inv}(x) = C_{ox}[V_G - 2\phi_B - V_{FB} - V_c(x)] - \sqrt{2\varepsilon_{sc}eN_a[V_c(x) + 2\phi_B]}$$

(2.10)

Integrating 2.9 from source (x = 0) to drain (x = L) using the above value for  $Q_{inv}(x)$  leads to

$$I_D = \frac{W}{L} \mu_n C_{ox} [(V_G - 2\phi_B - V_{FB})V_D - \frac{V_D^2}{2} - \frac{\sqrt{8\varepsilon_{sc}eN_a}}{3C_{ox}} ((V_D + 2\phi_B)^{3/2} - (2\phi_B)^{3/2})]$$

(2.11)

where L is the length of the device channel.

Equation 2.11 is valid as long as both ends of the channel are in strong inversion. For a sufficiently high drain bias, the potential difference between the drain end of the channel and the bulk will be dropped completely over the depletion layer and no inversion layer will be available at that end, i.e., the channel *pinches off* at the drain side. This defines the saturation drain voltage  $V_D sat$ , as the value of  $V_D$  for which  $Q_{inv}(x = L) = 0$ .

The value of  $V_{Dsat}$  can be derived equating  $Q_{inv} = 0$  at x = L in 2.10:

$$V_{Dsat} = V_G - 2\phi_B - V_{FB} + \frac{\varepsilon_{sc}eN_a}{C_{ox}^2} \left[ 1 - \sqrt{1 + \frac{2(V_G - V_{FB})Cox^2}{\varepsilon_{sc}eN_a}} \right]$$

(2.12)

The above derivation of  $I_D$  (Eq. 2.11) remains valid only as long as  $V_D < V_{Dsat}$ , called the linear region. Beyond pinch off the treatment of the current problem is quite complex (Chen, Ma, Kuo, Yu, and Dutton 1995). As all relevant measurements in this work are carried out in the linear region, this problem will not be discussed in detail here. However, for long enough devices, beyond pinch off the current essentially remains constant.

For very small drain bias  $V_D << (V_G - V_{FB} - 2\phi_F)$  one can consider the level of inversion being the same along the whole channel ( $Q_{inv}$  independent of x) and write the current-voltage relation in terms of the threshold voltage as

$$I_D \approx \frac{W}{L} \mu_n C_{ox} (V_G - V_T) V_D \tag{2.13}$$

In this low drain bias region the current-voltage relations are linear and the device is said to be operating in the *linear region*.

As mentioned earlier, an increasing drain bias causes the channel to pinch off at the drain end. In a simple approximation, it can be assumed that after  $V_D$  exceeds  $V_{Dsat}$  the current keeps constant (Brews 1978). Another simplification generally accepted is to assume the onset of pinch off to occur when the potential applied between gate an drain equals threshold, i.e.,  $V_{Dsat} = V_G - V_T$ . This leads to the traditional form for the current in the saturated region (Tsividis 1987)

$$I_{Dsat} = \frac{W}{2L} \mu_n C_{ox} (V_G - V_T)^2$$

(2.14)

According to this equation, in the saturated region, the current has a square law dependence upon the gate bias and does not depend upon the drain bias.

The above current-voltage relations are based on 2.9, which assumes that the current is mainly due to drift. In weak inversion this is not the case. In weak inversion most of the current is caused by carrier diffusion.

Diffusion occurs whenever the charge carriers are not uniformly distributed along the channel, that is, when carrier concentration gradients exist; then the thermal random motion of the carriers tends to cause the spreading out from regions of high concentration to regions of low concentration. The diffusion current can be written as

$$I_{diff}(x) = \mu_n W \frac{k_B T}{q} \frac{\partial Q_{inv}}{\partial x}$$

(2.15)

Assuming that in weak inversion the only significant component of the current is due to diffusion (Brews 1979) and noting that in dc steady state, the case of relevance for this work, the total current in the channel must be the same for all x along the channel and equal to the drain current. Therefore, it follows from the form of 2.15 that  $\partial Q_{inv}/\partial x$  must be a constant, i.e.,  $Q_{inv}$  versus x must be a straight line, leading to

$$I_D = W\mu \frac{k_B T}{q} \frac{Q_{inv}(x=0) - Q_{inv}(x=L)}{L}$$

(2.16)

The above two values of  $Q_{inv}$  can be found solving Poissons equation again, using an inversion layer concentration of the form 2.2 that depends on the coordinate x along the channel, and considering that the difference between the surface potential at the drain end and at the source end of the inversion layer must be equal to the drain voltage  $[\phi_S(x=L) - \phi_S(x=0) = V_D]$ . This leads to the following expression for drain current (Brews 1979)

$$I_D = \frac{W}{L} \mu Q_{inv}(0) \left( 1 - e^{-\frac{qV_D}{k_B T}} \right) k_B T$$

(2.17)

where  $Q_{inv}(0)$  is the inversion layer charge at the source end of the channel (Brews 1978),

$$Q_{inv}(0) = qN_A L_B \sqrt{2} \left( \sqrt{\frac{q\phi_S(0)}{k_B T} - 1 + \left(\frac{n_i}{N_A}\right)^2 e^{\frac{q\phi_S(0)}{k_B T}}} - \sqrt{\frac{q\phi_S(0)}{k_B T} - 1} \right)$$

(2.18)

where  $L_B$  is the bulk Debye length,  $L_B = (k_B T \varepsilon_{sc}/q^2 N_A)$ , and the band bending at the source end of the channel  $\phi_S(0)$  can be related to the gate bias by (Brews 1979)

$$\phi_S(0) = V_G - V_{FB} - \frac{k_B T}{q} \left( \frac{\varepsilon_{sc} t_{ox}}{\varepsilon_{ox} L_B} \right)^2 \left( \sqrt{1 + \frac{2\varepsilon_{ox} L_B}{\varepsilon_{sc} t_{ox}} \left( (V_G - V_{FB}) \frac{q}{k_B T} - 1 \right)} - 1 \right)$$

(2.19)

These equations lead to a drain current that increases exponentially with  $V_G$ . For drain biases  $V_D$  larger than a few  $(k_BT/q)$  the current in the sub threshold region will saturate (i.e., is independent of  $V_D$ ). Therefore, it is a matter of continuity to suppose that the pinch off condition also prevails in the sub threshold region when the current has saturated.

#### 2.2 Temperature Dependence

MOSFET characteristics are known to be strongly temperature-dependent (Ytterdal, Hurt, Shur, Park, Tsai, and Peatman 1996; Borzdov and Petrovich 1997; Chen, Ma, Kuo, Yu, and Dutton 1995). One of the parameters whose temperature dependence has been extensively studied is the mobility  $\mu$  of the charge carriers in the channel.

According to the Bloch theorem, in a perfect periodic potential, the electrons show a free electron-like behavior where no scattering is allowed. But in real semiconductors there are imperfections and scattering does occur. The most important sources of scattering are Coulomb centers, surface roughness and lattice vibrations (phonons). Each of them depicts a very particular temperature dependence.

Lattice vibrations are an inevitable source of scattering and dominate the scattering process near room temperature for high quality samples, i.e. with small interface roughness. In the range of inversion layer electron concentrations of  $N_{inv} = 0.5 - 5x10^{12}cm^{-2}$  and around room temperature, the mobility  $\mu$  is known to be proportional to  $T^{-a}$ , with 1 < a < 1.5. This behavior of mobility is generally assumed to be determined by phonon scattering (Ando, Fowler, and Stern 1982).

Surface roughness at the  $Si/SiO_2$  interface are expected to constitute a major cause of scattering at high electron concentrations. The surface roughness contributes a perturbation  $\delta V(x,y,z)$  to the potential energy in the inversion layer, which becomes more important as the transversal electrical field increases, i.e. at higher  $V_G$  and consequently larger inversion layer charge concentrations. After the calculations of Cheng and Sullivan (Cheng and Sullivan 1973) scattering by surface roughness is only weakly dependent on temperature.

Coulomb scattering is originated by charged centers near or in the inversion layer, for example, ionized dopant impurities or oxide charges near or at the  $Si/SiO_2$  interface. This scattering

mechanism is known to lead to a scattering probability that increases as the kinetic energy of the carriers decrease (Ando, Fowler, and Stern 1982). As the carrier density in the inversion layer increases, however, the screening effect becomes important. The screening effect is reduced as the kinetic energy of the carriers increases. Therefore, the actual temperature dependence of Coulomb scattering is determined by the relative importance of these two effects.

As a result, the scattering mechanism that will dominate at a given temperature depends on the quality of the sample and on the amount of inversion (Lee, Choi, Sim, and Kim 1991). For undoped or lightly doped samples with negligible oxide charge the mobility increases monotonically as the temperature decreases, since Coulomb scattering is negligible and the lattice scattering decreases with temperature. However, for doped samples the mobility shows a peak at low temperatures and then decreases, showing that coulomb scattering at ionized impurities is the dominant scattering mechanism for doped samples at low temperatures. If the charge concentration in the oxide is high, coulomb scattering at the oxide charge near the  $Si/SiO_2$  interface may become important. For high inversion layer concentrations, screening becomes effective. In this situation there are large transversal electrical fields, and if the  $Si/SiO_2$  interface is of poor quality, surface roughness can become the dominating scattering mechanism (Takagi, Toriumi, Iwase, and Tango 1994).

Another important point is that at low temperatures, Boltzmann statistic does not hold anymore and Fermi-Dirac statistics must be used. Fermi-Dirac statistics leads to very complex analytic expressions and is prohibitive for practical numerical analysis. One simplification usually done, called the 0 Kelvin approximation, is to approximate the Fermi-Dirac distribution by a step function at the Fermi level. At 0 Kelvin the carriers are frozen out, leading to the Fermi level lying between the valence (conduction) band edge and the acceptor (donors) energy levels, and the acceptor (donor) atoms not ionizing. However, at high doping concentrations the acceptor (donor) energy levels come very close the valence (conduction) band and the energy needed to excite the doping atoms becomes vanishingly small. Hence, for degenerated semiconductors mobile carriers are available even at vanishingly small temperatures (Wu and Anderson 1974).

For an nMOSFET in the 0 Kelvin temperature region, if sufficient gate bias is applied, the energy of the conduction band edge can be reduced below that of the edge of the quasi-Fermi level of the degenerate source and/or drain. In this case, electrons are injected into the inversion layer. Furthermore, at low temperatures, the potential in the bulk  $\phi_B$  is closer to the valence band edge than at room temperature. Therefore, the total band bending needed to create the inversion layer is improved. This process leads to an increasing threshold voltage  $V_T$  with decreasing temperature. On the other hand, the channel turns on more abruptly, decreasing the sub threshold slope (Hanamura, Aoki, Masuhara, Minato, Sakai, and Hayashida 1986).

Although these very important differences between the operation of MOSFETs at room and cryogenic temperatures do exist, Hu and Anderson (Wu and Anderson 1974) have found that the expression for the drain current has the same form for the two temperature ranges. This is true as long as the following conditions are fulfilled:

1. The impurity concentrations at the source and drain are very high and thus these are degenerated. This insures that electrons are available, i.e. not frozen out, even in the 0 K approach.

#### 2. There are no potential barriers between the channel and the drain and source regions.

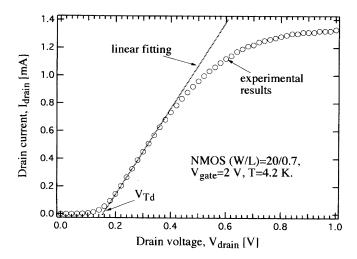

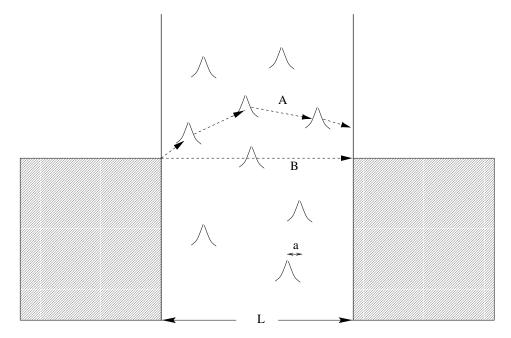

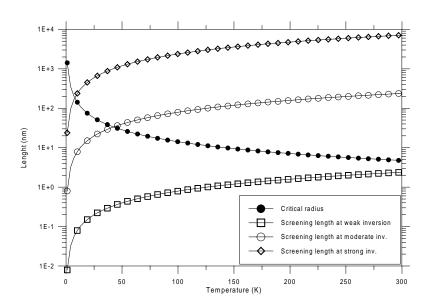

In contrast, if the gate does not overlap source and drain or if the gate oxide thickness is increased in the overlap regions, potential hills will occur in the channel. Although these barriers will be small to affect current-voltage characteristics at room temperature, at low temperature they can prevent current flow until a minimum drain voltage ( $V_{Td}$ ) is applied. At voltages very near  $V_{Td}$ , the I-V characteristics is expected to be quite non-linear, but monotonically increasing with increasing  $V_D$ , as shown in Fig. 2.3 (Gutierrez 1995). This is valid as long as the channel is long enough, the quantization of energy states in the x-direction along the channel can be neglected, and the capacitance of the channel is large enough so that the shift in channel surface potential by charging it with one extra electron is vanishingly small. If this does not hold, the picture can change dramatically, as discussed in section 5.1 (resonant tunneling) and section 5.5 (Coulomb Blockade).

**Figure 2.3:** Measured  $I_D \times V_D$  characteristics of nMOS LDD transistor with L=0.7  $\mu m$  operated at 4.2 K showing the Drain Threshold Voltage  $V_{Td}$  due to lack of overlapping between gate and drain and/or source. After (Gutierrez, 1995).

#### 2.3 Channel Carrier Quantization

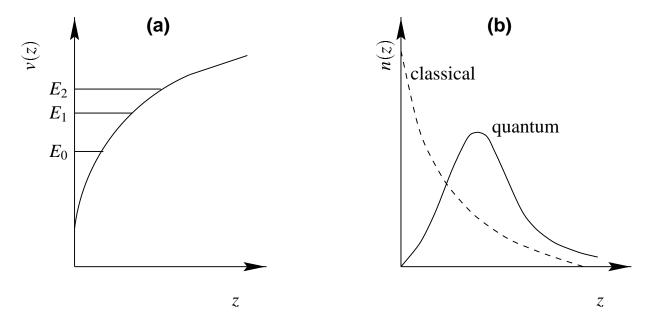

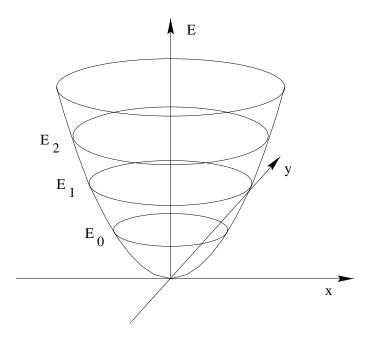

As shown in Fig. 2.4, the bandbending of the semiconductor in the inversion layer is strong enough to produce a potential well. Its width in the direction perpendicular to the surface is small compared to the wavelengths of the carriers. Thus, the energy levels of the electrons are grouped into electric subbands, each of which corresponds to a quantized level for motion in the direction perpendicular to the surface, with a continuum for motion in the plane parallel to the surface.

A rigorous treatment of electron states in the inversion layer requires complex numerical and self-consistent solutions of the Poisson and Schrödinger equations.

**Figure 2.4:** Quantization of the inversion charge. (a) shows the potential well and the quantized energy levels for a representative Si surface. (b) shows the corresponding classical and quantum-mechanical charge densities.

One of the simplest approximations, the effective-mass approximation, treats the electrons as though they had masses characteristic of a conduction-band minimum, neglecting nonparabolicity and coupling to other band extrema. Then one can use a kinetic energy operator of the form (Siggia and Kwok 1970)

$$\hat{T} = \frac{\hbar^2}{2} \sum_{i,j} w_{i,j} \frac{\partial^2}{\partial x_i \partial x_j}$$

(2.20)

where the  $w_{i,j}$  are the elements of the reciprocal effective-mass tensor for the particular conduction band minimum being observed.

If no bias is applied between drain and source, the potential is a function of z only, and the wave function can be written as the product of a Bloch function, a z-dependent factor, and a plane-wave factor representing the free motion in the xy-plane. This leads to constant-energy parabolas above the level  $E_i$  which is the bottom of the i-th subband, where the electronic wave function for the i-th subband is of the form (Stern and Howard 1967)

$$\Psi_i(x, y, z) = \zeta_i(z)e^{i\theta z}e^{ik_1x + ik_2y}u_{\alpha}$$

(2.21)

where  $k_1$  and  $k_2$  are measured relative to the band edge,  $\theta$  depends on  $k_1$  and  $k_2$ ,  $u_{\alpha}$  is the Bloch function for the bottom of the conduction band valley being considered, and  $\zeta_i(z)$  is the solution of the Schrödinger equation

$$\frac{d^2\zeta_i}{dz^2} + \frac{2m_3}{\hbar^2} [E_i + e\phi_i(z)] = 0$$

(2.22)

where  $m_3$  is the effective mass in the direction perpendicular to the  $Si/SiO_2$  interface (z-direction). As the electrons are bound in the inversion layer, it is required that  $\zeta_i(\infty) = 0$ . In addition, it is required that  $\zeta_i(z)$  vanish at the surface, where z = 0. This is a good approximation for the  $Si/SiO_2$  interface, for which the potential barrier for electrons is approximately 3 eV. More realistic boundary conditions which do not require that  $\zeta_i(z)$  vanish at the surface will lead to energy levels with reduced energies and increased energy-level splittings, but the deviations are expected to be small. More recent calculations, which do not impose this restriction, do not show significant deviations in the results. See, for instance, (Janik and Majkusiak 1998); (Spinelli, Benvenutti, and Pacelli 1998) or (Jallepalli, Shih, Pinto, Maziar, and Jr. 1997).

Each eigenvalue  $E_i$  found from the solution of 2.21 is the bottom of a continuum of levels called a subband, with energy levels given by

$$E_i(\vec{k}) = E_i + \frac{\hbar^2 k_1^2}{2m_1} + \frac{\hbar^2 k_2^2}{2m_2}$$

(2.23)

where  $m_1$  and  $m_2$  are the principal effective masses for motion parallel to the surface, which can be obtained in a straightforward way from the bulk masses (Stern and Howard 1967). Values for these quantities and for the mass  $m_3$  for motion perpendicular to the surface, used in 2.21, are given in Table 2.1 for the (100) surface orientation, the surface orientation of the devices used in this work.

| Valley       |         | Lower | Higher |

|--------------|---------|-------|--------|

| Degeneracy   | $n_{v}$ | 2     | 4      |

| Normal mass  | $m_3$   | 0.916 | 0.190  |

| Longitudinal | $m_1$   | 0.190 | 0.190  |

| masses       | $m_2$   | 0.190 | 0.916  |

**Table 2.1:** Parameters for the (100)-Si-Surface.

Since in this approach the kinetic energy of the motion perpendicular to the surface is of the form  $\hbar^2 k_z^2/2m_3$ , the valleys which present the highest mass for motion perpendicular to the surface have the lowest kinetic energy and the lowest energy levels. The subbands arising from these valleys are labeled with indices 0,1,2, ... The second ladder of subbands, arising from the valleys with the lower mass for motion perpendicular to the surface, are labeled 0', 1', 2', ...

The potential  $\phi(z)$  which appears in 2.22 is the solution of Poissons equation

$$\frac{d^2\phi(z)}{dz^2} = -\frac{1}{\varepsilon_{sc}} \left[ \rho_{depl}(z) - e \sum_{i} N_i \zeta_i^2(z) \right]$$

(2.24)

where  $\varepsilon_{sc}$  is the permittivity of the semiconductor,  $N_i$  is the carrier concentration in the *i*th subband, given by

$$N_{i}(\vec{k}) = \frac{n_{vi}m_{di}k_{B}T}{\pi\hbar^{2}}F_{0}[\frac{E_{F} - E_{i}}{k_{B}T}]$$

(2.25)

$F_0(x) = ln(1 + e^x)$ ,  $n_{vi}$  and  $m_{di}$  are the valley degeneracies and the density-of-states effective mass per valley, given in Table 2.1.  $\rho_{depl}$  is the charge density of the depletion layer.

The second term on the right hand side of 2.24 is the charge density in the inversion layer

$$\rho_{inv}(z) = -e \sum_{i} N_i \zeta_i^2(z)$$

(2.26)

where  $\zeta_i$  is the normalized eigenfunction corresponding to the *i*th solution of 2.22. The function  $g_0(z) = |\zeta_0(z)|^2$  is shown for a representative case in Fig. 2.4(b).

Because of the way in which the Schrödinger and Poisson equations are coupled, it is necessary in general to solve these equations numerically to obtain self-consistent results, as described below.

It is, however, possible to find approximate analytical results for some simple limiting cases. The simplest approximation is to replace the potential  $\phi(z)$  in 2.22 by  $-F_sz$  for z > 0 and by an infinite barrier for z < 0.  $F_s$  is the surface electrical field. This is the so called "triangular-potential approximation". It leads to Airy equation with the solutions (Stern 1972):

$$\zeta_i(z) = Ai \left[ \left( \frac{2m_3 e \phi_s}{\hbar^2} \right)^{\frac{1}{3}} \left( z - \frac{E_i}{eF_s} \right) \right]$$

(2.27)

$$E_i \cong \left(\frac{\hbar^2}{2m_3}\right)^{\frac{1}{3}} \left(\frac{2}{3}\pi e\phi_s(i+\frac{3}{4})\right)^{\frac{2}{3}}$$

(2.28)

The exact eigenvalues for  $E_i$  have  $i + \frac{3}{4}$  in 2.28 replaced by 0.7587, 1.7540 and 2.7525, respectively (Stern 1972).

The triangular-potential approximation may be a reasonable approximation when there is a little or no charge in the inversion layer (weak inversion), but fails when the charge density per unit area in the inversion layer is comparable to or exceeds that in the depletion layer (strong inversion) (Stern 1972).

When only one subband is occupied, that is, in the electric quantum limit, a variational approach gives a good estimate for the energy of the lowest subband. Fang and Howard (Fang and Howard 1966) used the trial eigenfunction

$$\zeta_0(z) = \left(\frac{1}{2}b^3\right)^{\frac{1}{2}} z e^{\frac{-bz}{2}} \tag{2.29}$$

with a single undetermined parameter b. The energy of the lowest state is found to be

$$E_0 = \frac{\hbar^2 b^2}{8m_3} + \frac{3e^2}{\varepsilon_{sc}b} \left[ N_{depl} + \frac{11}{16} N_{inv} - \frac{2}{b} (N_A - N_D) \right]$$

(2.30)

Approximate energy levels for the excited states can be obtained in the electric quantum limit by treating the inversion-layer potential and the curvature of the depletion potential as perturbations. The inversion-layer charge density is assumed to be a sheet located a distance  $z_0$  from the surface.

The approximated analytical results described above may be used as an initial estimate for the potential  $\phi(z)$  to solve Eqs. 2.22 and 2.24 successively with a numerical algorithm until the output potential from 2.24 agrees with the input potential in 2.22 to within specified limits. This is the so called self-consistent method in the effective mass approach.

Because of the form of the kinetic energy operator in 2.20, the results obtained with the effective mass approach do not apply to inversion-layer energy levels arising from a warped (non-parabolic) bandstructure like the valence band of Silicon.

One method to overcome the limitations of the effective mass approach is to include non-parabolicity corrections for the dispersion relation in the self-consistent solution of 2.22 and 2.24 (Troger, Kosina, and Selberherr 1997). Following the effective mass approach and including a non-parabolicity correction term in the bulk dispersion relation

$$\varepsilon_i(1+\alpha\varepsilon_i) = \frac{\hbar^2 k_3^2}{2m_3} + \frac{\hbar^2 k_1^2}{2m_1} + \frac{\hbar^2 k_2^2}{2m_2}$$

(2.31)

one has to solve the Schrödinger equation, which now, unlike 2.20, has a kinetic energy operator that does not allow to separate the energy term due to the in-plane transport. It will introduce a dependence on the in-plane wave vectors  $k_1, k_2$  of both the eigenenergies and the wave functions (Troger, Kosina, and Selberherr 1997):

$$\hat{T} = \frac{1}{2\alpha} \left[ -1 + \sqrt{1 + 2\alpha\hbar^2 \left(\frac{k_1^2}{m_1} + \frac{k_2^2}{m_2} + \hat{G}\right)} \right]$$

(2.32)

$$\hat{G} = -\frac{\partial}{\partial z} \frac{1}{m_3} \frac{\partial}{\partial z} \tag{2.33}$$

This complicates the problem and increases the computational power needed to solve the equations.

The group of Jallepalli (Jallepalli, Shih, Pinto, Maziar, and Jr. 1997) has done full band calculations and did observe remarkably good agreement between the full band and the effective-mass calculations of electron subband dispersions and wave functions in n-MOS inversion layers. The only significant difference between the two was found to be a small doping-dependent shift between the subband edges.

One of the most important aspects of the inversion layer quantization in the scope of this work is the possibility of population of excited subbands. In the 0 K approximation, only the ground subband is occupied at moderate inversion layer charge densities (up to  $3x10^{12}cm^{-2}$  for  $N_A - N_D = 10^{15}cm^{-3}$ ) (Stern 1972). For higher inversion layer charge densities the first excited subband can become occupied. As the separation between the subbands increases with increasing inversion layer density (Moglestue 1986), the population of a second excited subband at low temperature is not expected. Another important feature is the pinning of the Fermi level to the bottom of the first excited subband after they cross. The pinning is a consequence of the increased density of states after the second subband is occupied (Ando, Fowler, and Stern 1982; Hänsch, Vogelsang, Kircher, and Orlowski 1989). As the temperature is increased, inversion-layer electrons will be excited to higher subbands, leading to an increasing inversion layer contribution to the potential well and a larger average  $z_{av}$  distance of the electrons from the surface.

At room temperature, an increasing space charge (increasing  $V_G$ ), will lead to a decreasing  $z_{av}$ , because of the increasing average field seen by the electrons, which increases the bandbending and overpowers the increase that might have been expected when the higher subband is occupied.

If a large source drain bias  $V_{DS}$  is applied, electrons can obtain sufficient energy in the longitudinal electric field to be transferred to an excited subband, as observed by the group of Neugebauer (Neugebauer, Landwehr, and Hess 1978). These authors observed Negative Differential Resistance (NDR) in nMOSFET of (100) surface orientation and suggested that the origin are heated electrons transferred from the twofold to the fourfold degenerate subband system, which has a greater effective mass in the channel direction and hence a lower mobility.

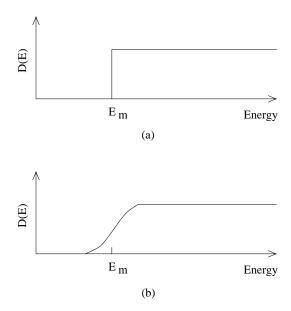

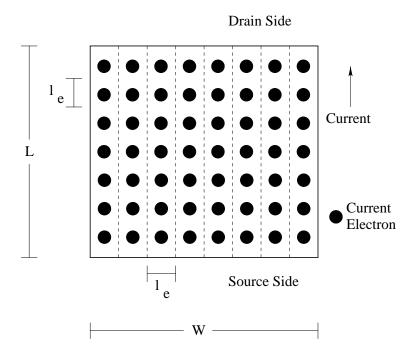

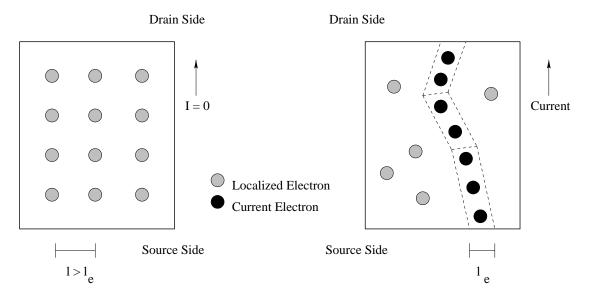

Other important aspects of inversion layer quantization are its impact on the threshold voltage  $V_T$ , transconductance, and on the capacitance of the MOS system. The shift of the carrier concentration peak away from the interface results in an increase in the effective oxide thickness (Jallepalli, Shih, Pinto, Maziar, and Jr. 1997; Ip and Brews 1998). This increase is also manifested as a lower transconductance and a lower quasi-static capacitance in strong inversion. Quantization also predicts an increased  $V_T$ , when compared to the classical theory. The first reason is that, as can be seen from Fig. 2.4, the ground state for electrons,  $E_0$ , is formed above the bottom of the conduction band. The second reason for the phenomenon is the reduction in the density of states in the inversion layer. In the 3-D transport system, the density of states increases continuously from the bottom of the conduction band. In the 2-D transport system, on the other hand, it changes in a stepwise manner, and there are fewer states even above the ground state than those in the 3-D transport system (Hareland, Jallepalli, Chindalore, Shih, Jr., and Maziar 1997). So the Fermi level has to be closer to the ground state in order to induce the inverted charges.

It is important to note that the preceding discussion of the subband structure is within the

Hartree approximation, which does not account for many-body effects such as exchange and correlation. This approximation is valid when the average kinetic energy of electrons is much larger than the average interaction energy, that is, when the electron concentration is sufficiently high (Ando, Fowler, and Stern 1982).

#### 2.4 Process Technology

The devices used in this research work are processed using an unique approach, developed along the years at the university of Dortmund. This method applies only conventional optical lithography and enables the fabrication of structures with a minimum line-width down to 30 nm without the requirement of expensive and time consuming techniques like e-beam writing or molecular beam epitaxy (MBE). Below an overview of the technique and the parameters of relevance to this work are given. A more detailed description of the process can be found in (Horstmann, Hilleringmann, and Goser 1996) or (Horstmann, Hilleringmann, and Goser 1997).

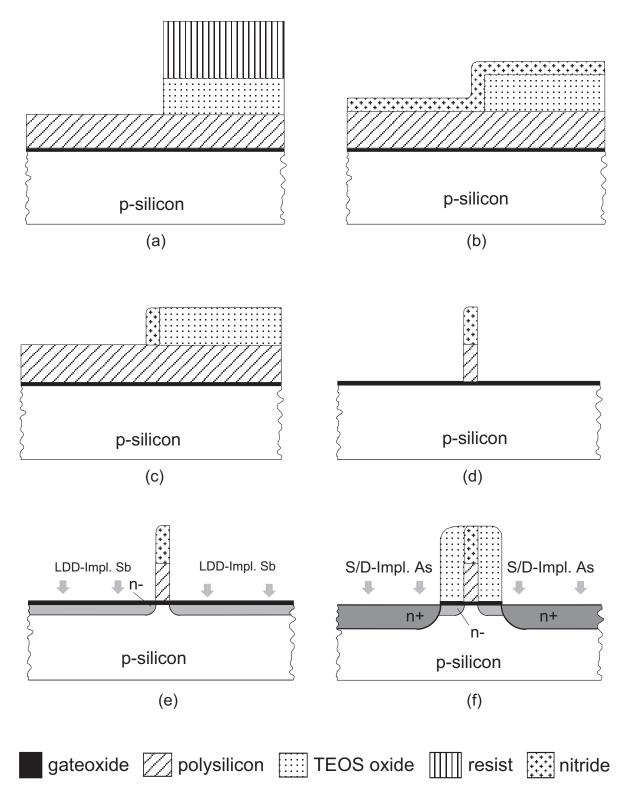

The process is based on a sidewall-etchback technique similar to the one used for the definition of the spacers in conventional MOS-Transistors, and runs on a conventional  $0.8 \,\mu\text{m}$ -CMOS-technology line.

The first step consists in depositing a polysilicon layer on the top of the thermally grown thin gate-oxide-film. After that, a sacrificial oxide layer is deposited and structured by dry etching, applying conventional optical lithography as shown in Fig. 2.5(a). The conformal deposition of a nitride layer follows, as depicted in Fig. 2.5(b). This nitride layer is etched back anisotropically, leaving a nitride spacer surrounding the oxide (step (c) in Fig. 2.5). This nitride spacer is used as a masking material for the definition of the transistor gates. Since the thickness of the nitride layer determines the width of the nitride spacer, the gate length is given by the nitride layer thickness. After the selective removal of the remaining sacrificial oxide layer, the nitride mask is transferred into the polysilicon layer, as depicted in part (d) of Fig. 2.5. This step is performed using anisotropic dry etching in the Reactive Ion Etching (RIE)-mode with chlorine chemistry.

For the Lightly Doped Drain regions, antimony is implanted, as shown in Fig. 2.5(e). Antimony is the material of choice because of its high mass, which allows to a low implantation range and diminished dopant diffusion in the subsequent thermal annealing steps. As a 7 degree tilt angle implantation method is used, the wafers are rotated four times during the implantation process to compensate the shadowing effect of the gate electrode. Finally, the oxide spacers are defined and the source/drain arsenic implantation is performed (step (f) in Fig. 2.5). Arsenic is chosen because of its high solubility in silicon.

**Figure 2.5:** The processing of sub-100nm-devices at the Department for Electrical Engineering, University of Dortmund. For a detailed explanation of the individual steps, please refer to the text.

# 3. Samples and Experimental Setup

In this chapter the layouts of the samples investigated are presented and the sample preparation is described. The main technological process parameters are given and the experimental setup used for carrying out the measurements is introduced.

Measurements have been carried out at temperatures between 300 mK and 35 K, and at room temperature. Low temperature measurements were carried out using a  ${}^{4}He$  cryostat with a single  ${}^{3}He$  insert from Oxford Instruments, or using simple, self-made  ${}^{4}He$  bath cryostats. The measurements in high magnetic fields were carried out using the  ${}^{3}He/{}^{4}He$  cryostat together with a superconducting coil magnet. This magnet can provide magnetic fields up to B=17 T.

#### 3.1 Sample Layout and Parameters

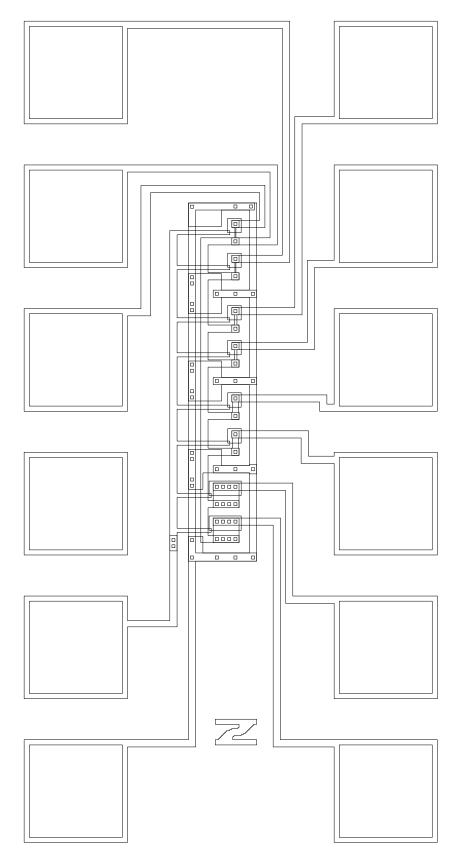

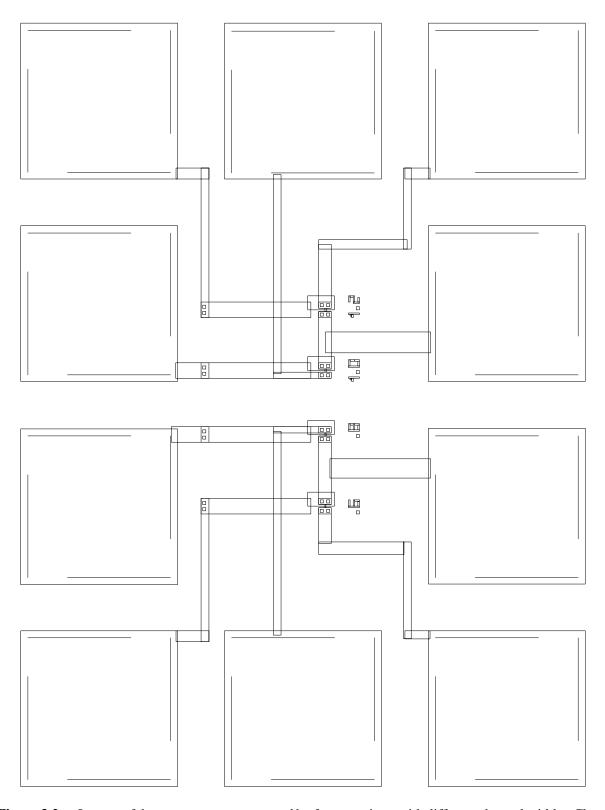

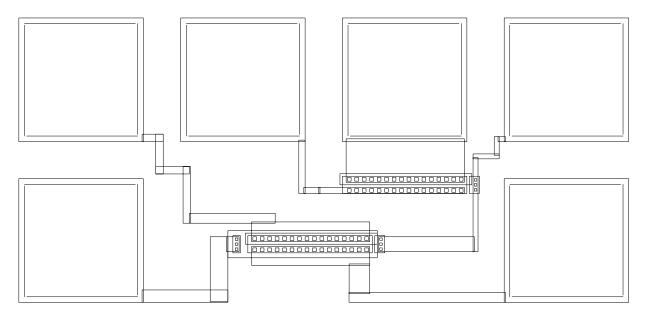

The layout of the transistors studied is shown in figures 3.1, 3.2 and 3.3. The first test structure (Fig. 3.1) is composed by 8 transistors with 4 different channel widths. For the mask set CTC 17 the channel widths are  $1.0 \ \mu m$ ,  $2.5 \ \mu m$ ,  $6.0 \ \mu m$  and  $25 \ \mu m$ . For the mask set CTC 16 one has channel widths of  $4.0 \ \mu m$ ,  $5.5 \ \mu m$ ,  $12.5 \ \mu m$  and  $25 \ \mu m$ . The sources of all transistors are connected to a common source pad. Similarly, the gates are all connected to a common pad. Each transistor is individually operated using separate drain pads. The second test structure (Fig. 3.2) is composed by 4 transistors, each with a different channel width:  $1.2 \ \mu m$ ,  $1.0 \ \mu m$ ,  $0.8 \ \mu m$  and  $0.6 \ \mu m$ . In this arrangement every transistor has one separate pad for driving drain and gate. The source pads are shared between two transistors: one by the  $1.2 \ \mu m$  and  $1.0 \ \mu m$  wide transistors and the other by the  $0.8 \ \mu m$  and  $0.6 \ \mu m$  wide transistors. The last test structure (Fig. 3.3) constitutes of 2 transistor with the same channel width of  $100 \ \mu m$ . If a CMOS process is used, one of them will be a n-type-transistor and the other a p-type-transistor. These transistors share a common gate pad, while other contacts are connected to separate pads.

As described in section 2.4, the channel length is not defined by the layout. The thickness of a nitride layer deposited in the particular process technology used defines the channel length. For the wafers used to obtain the experimental results reported in this work, the technological parameters of relevance are summarized in tables 3.1 and 3.2. The gate oxide thickness  $(t_{ox})$  is measured by an ellipsometer.  $L_{design}$  is the design channel length, i. e., the width of the nitride spacer, measured using a Scanning Electron Microscope (SEM). The effective channel length  $(L_{eff})$ , the Sb-dopant concentration in the LDD region (LDD Conc., in  $cm^{-3}$ ) and its depth (LDD Depth), the B-dopant concentration in the channel at the  $Si/SiO_2$  interface (Surf. Conc., in  $cm^{-3}$ ) as well as the depth of the source and drain regions (D/S Depth) are values estimated by means of process simulation with the two-dimensional process simulator DIOS (ISE - Integrated

**Figure 3.1:** Layout of the test structure composed by four transistor pairs with different channel widths. The gates are driven by a common gate pad, and the sources contacted through a common source pad. The transistors can be individually operated over the isolated drain pads.

**Figure 3.2:** Layout of the test structure composed by four transistor with different channel widths. Channel widths are  $1.2 \mu m$ ,  $1.0 \mu m$ ,  $0.8 \mu m$  and  $0.6 \mu m$ . There are isolated pads for driving the individual gate and drain contacts. All transistors gates are driven by a common gate pad. The source pads are shared between two transistors.

**Figure 3.3:** Layout of the test structure composed by two transistors with the same channel width  $W = 100 \ \mu m$ . Transistors gates are driven by a common gate pad. All other contacts are connected to isolated pads.

Systems Engineering AG 1994), for room temperature.

After processing, the individual test structures are split from the wafer using a conventional diamond dicing saw. Next, the dies are cleaned with acetone and submited to a 15 min. furnace annealing at 150 C. The dies are then attached to gold plated ceramic dual in line packages (DIP) using a silver epoxy adhesive. The chip-pads are bonded to the package pins using an ultra-sonic bonder with aluminum wiring. Good bulk contact is ensured by attaching the dies to the gold package plating using a silver basis adhesive. This contact could be verified by measuring the diodes formed by the source-bulk and drain-bulk junctions (at room and at low temperature).

After bonding, samples are only handled with the user connected to ground through an antistatic-bracelet, to assure the integrity of tests structures, specially of the very thin gate oxide.

Devices with design channel lengths  $L_{design}$  between 30 nm and 120 nm and channel widths W between 0.6  $\mu m$  and 100  $\mu m$ , processed on (100) silicon as described in the previous chapter, are studied at low (0.3K < T < 35K) and room temperature. The samples have been processed in different runs, with gate oxide thickness  $(t_{ox})$  ranging from 4.0 nm to 8.7 nm. The depths of the lightly doped drains (LDD) are between 10 nm and 13 nm. For the  $t_{ox}$ , L and LDD depth values of the particular samples, please refer to tables 3.1 and 3.2. For the sake of comparison some devices without LDD have also been processed. For these devices the design channel length was  $L_{design} = 120nm$ , and the effective channel length is estimated to be  $L_{eff} \approx 50nm$ , by numerical process simulations performed using DIOS (ISE - Integrated Systems Engineering AG 1994).

Devices with micrometer scale channel lengths, processed on the same wafers as the sub-100 nm devices, have also been measured.

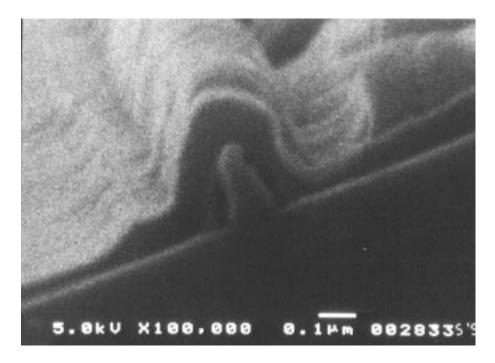

A scanning electron microscope (SEM) photography of a device cross section is shown in

**Figure 3.4:** Scanning electron micrography showing a device cross section. The polysilicon gate electrode is  $\approx 50nm$  in length and  $\approx 220nm$  in height. The top layer is  $SiO_2$ .

Fig. 3.4. The 50 nm long gate electrode with the passivation oxide on the top can be clearly seen.

# 3.2 Experimental Setup for Measurements at Low Temperature

For the charge transport measurements at liquid Helium temperatures three different setups were employed. The theory necessary to understand the behavior of MOSFET at cryogenic temperatures was given in section 2.2.

In the first measurement setup, present at the *Lehrstuhl für Werkstoffe der Elektrotechnik*, *Fakultät für Elektrotechnik*, *Ruhr-Universität Bochum*, the samples were loaded into a  ${}^4He$  cryostat with a single  ${}^3He$  insert from Oxford Instruments, model *Spectromag with Heliox*( ${}^3He$ )-insert. This cryostat allows top loading into a  ${}^3He$  or  ${}^4He$  vessel.

If the sample is immersed in the  ${}^4He$  bath held at atmospheric pressure, the sample will be in thermal equilibrium with the bath after few minutes (at the  ${}^4He$  boiling temperature, 4.2 K). The samples are slowly loaded to avoid a thermal shock, and a wait period of at least 15 min. after the sample was immersed into the bath was required, before proceeding with the electrical measurements.

To allow experiments at lower temperatures, the cryostat is equiped with a sorption pump (sorb) for the condensation of the liquid  ${}^{3}He$ , making it possible to reach a base temperature

| Wafer        | 366/3                | 366/13               | 377/3                | 397/2                | 397/6                |

|--------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| $L_{design}$ | 53 nm                | 54 nm                | 72 nm                | 53 nm                | 32 nm                |

| $L_{eff}$    | 48 nm                | 49 nm                | 67 nm                | 49 nm                | 28 nm                |

| Spacer Width | 110 nm               | 110 nm               | 110 nm               | 100 nm               | 100 nm               |

| $t_{OX}$     | 8.7 nm               | 7.0 nm               | 4.4 nm               | 4.9 nm               | 4.7 nm               |

| Surf. Conc.  | $1.0 \times 10^{18}$ | $8.0 \times 10^{17}$ | $8.5 \times 10^{17}$ | $7.7 \times 10^{17}$ | $7.7 \times 17^{17}$ |

| LDD Conc.    | $1.5 \times 10^{18}$ | $1.2 \times 10^{18}$ | $1.5 \times 10^{18}$ | $1.2 \times 10^{18}$ | $1.2x10^{18}$        |

| LDD Depth    | 10 nm                | 11 nm                | 13 nm                | 10 nm                | 10 nm                |

| D/S Depth    | 120 nm               |

**Table 3.1:** Technology Parameters for the NMOS Wafers.

| Wafer        | 413/6                | 430/1                | 430/3                | 430/5                | 430/7                |

|--------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| $L_{design}$ | 120 nm               | 82 nm                | 80 nm                | 49 nm                | 48 nm                |

| $L_{eff}$    | 50 nm                | 60 nm                | 60 nm                | 45 nm                | 45 nm                |

| Spacer Width | n.a.                 | 110 nm               | 110 nm               | 110 nm               | 110 nm               |

| $t_{OX}$     | 4.7 nm               | 3.8 nm               | 8.3 nm               | 4.0 nm               | 8.1 nm               |

| Surf. Conc.  | $1.1 \times 10^{18}$ | $1.0 \times 10^{16}$ | $1.0 \times 10^{16}$ | $8.2 \times 10^{17}$ | $8.0 \times 10^{17}$ |

| LDD Conc.    | n.a.                 | $9.0x10^{17}$        | $1.6 \times 10^{18}$ | $1.4 \times 10^{18}$ | $1.6 \times 10^{18}$ |

| LDD Depth    | n.a.                 | 12 nm                | 10 nm                | 12 nm                | 10 nm                |

| D/S Depth    | 90 nm                | 120 nm               | 120 nm               | 120 nm               | 120 nm               |

**Table 3.2:** Technology Parameters for the NMOS Wafers (cont.).

lower than 0.3 K. The temperature of the bath is then held constant by a manifold pumping and needle valves system, that controls the vessel pressure. With this system the temperature can be held constant for a few hours, depending on the power dissipated by the sample. A typical value of the power dissipated by the sample during measurement was 1 nW  $(100nA \times 10mV)$ . The cooling power of the system is much greater  $(120 \mu W, \text{minimum})$ .

During the measurements the temperature was continuously monitored by a sensor in contact with the sample socket. The temperature sensed with an accuracy of at least 0.01 K if no magnetic field is applied, and of at least 0.1 K if high magnetic fields was present. As well as offering mechanical valve control, the cryostat also incorporated a still heater control and automated temperature monitoring, making it possible to carry out measurements at a wide temperature range.

The cryostat is equiped with a  $Nb_3Sn$  DC superconducting magnet that allows the application of magnetic fields up to 17 T, with a homogeneity better than 0.1% over the whole sample area. The manufacturer guarantees the persistence of the magnetic field to be better than 0.01%/hour. The magnetic field strength was always monitored during measurements. The magnet operating current, which brings up the magnetic field, is remotely controlled through a microcomputer connected to the current control unit via the GPIB interface. The accuracy of the applied field is

better than 0.001 T.

In order to avoid the damaging of the very sensitive devices, all sample pins are connected to ground during the loading into the cryostat and cooling down procedure.

The equipment for electrical measurements is outside the cryostat, at room temperature, and the cryostat is connected to the same electrical ground as the measurement equipment. Measurements were carried out using standard lock-in techniques, with a dual phase lock-in amplifier supplied by Stanford Research Systems, model SR830 (Stanford Research Systems 1996). This lock-in amplifier has a sensitivity of 2 nV to 1 V, a gain accuracy of  $\pm 1\%$ , an absolute phase error of <  $1^{\circ}$  and a relative phase error <  $0.001^{\circ}$ .

The second measurement setup, where most measurements were carried out, is composed by a HP4156A precision semiconductor analyzer (Yokogawa-Hewlet-Packard. Ltd. 1995) and a self-built <sup>4</sup>He bath cryostat. The measurements were carried out taking advantage of the low-temperature gases facility of the Lehrstuhl Experimentelle Physik II, Institut für Physik, Universität Dortmund.

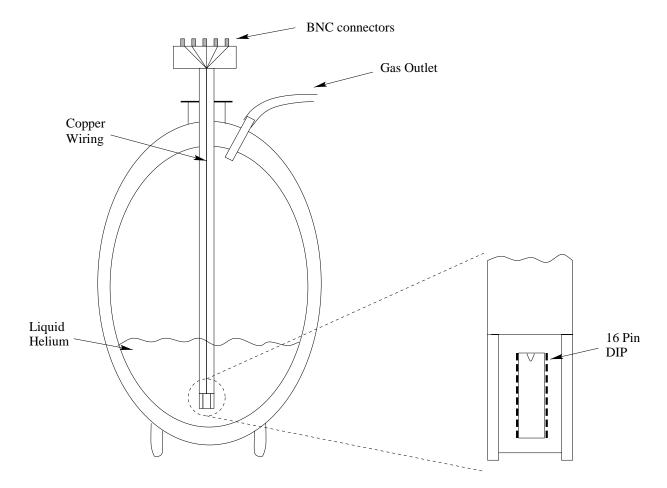

The cryostat consists basically of an 100 liter can filled with  ${}^4He$  and a sample-carrier for top loading. The sample-carrier consists of a steel tube with a 16-pin socket at its bottom end, where the sample, mounted and bonded on a ceramic DIP package, can be attached. The tube is made out of high quality steel with low thermal conductivity. There are two isolated copper wires to each socket pin. BNC connectors are provided at the top-end. A schematic representation of the experimental setup is shown in 3.5. To ensure temperature stability, the sample is immersed into the liquid  ${}^4He$  bath and the system is held at atmospheric pressure during the whole measurement. Hence, the sample is kept at the stable  ${}^4He$  boiling temperature (4.2 K). For economic reasons, the evaporated  ${}^4He$  is recovered and liquefied again. Also in this measurement setup, the sample is slowly loaded and sample pins are kept grounded during the whole cool down procedure.

The sample is then electrically connected to the HP4156A using triaxial cables. There are independent connections for applying the electrical signals (force) and to perform the measurements (sense), that is, Kelvin connections are employed. Cryostat and measurement equipment are connected to the same electrical ground.

The HP4156A offers a measurement resolution of  $2\mu V$  and accuracy of  $\pm (0.01\% + 200\mu V)$  for the voltage range up to 2.2V. For the range 2.2V < V < 22V measurement resolution is  $20\mu V$  and accuracy  $\pm (0.01\% + 1mV)$ . Voltage set accuracy is  $\pm (0.02\% + 400\mu V)$  for the 0V < V < 2.2V range, and  $\pm (0.02\% + 3mV)$  for the 2.2V < V < 22V range. The minimum output resolution is  $100\mu V$ . Current measurement accuracy is  $\pm (0.5\% + 0.4pA)$  for the 1 nA Range. For the 10 nA range, measurement accuracy is  $\pm (0.5\% + 2pA)$ . The 100 nA range has an accuracy of  $\pm (0.1\% + 20pA)$ , and finally, the last range of relevance for this work, the  $1\mu A$  range, has an accuracy off  $\pm (0.1\% + 200pA)$ . The High Resolution Source/Monitor Units (HRSMUs) were always used.

In both experimental setups described, the smallest drain voltage that could be applied during measurement was 0.1mV. This value corresponds to the thermal voltage at a temperature  $T \approx 1.1K$ . Hence, the electron gas is slightly heated at the lowest temperatures. It should be again noted that, as described in chapter 4, the pattern does not change neither with drain voltage nor with temperature, and this is not expected to have dramatic consequences.

**Figure 3.5:** Schematic representation of the experimental setup: the sample is immersed into liquid Helium. The gas outlet is used for recovering the evaporated Helium, and the system is kept at atmospheric pressure. The sample is attached to a 16-Pin DIP socket. Each socket pin is connected to two BNC connectors using isolated copper wires, to allow the implementation of Kelvin connections up to the measurement apparatus.

A third measurement setup, very similar to the one just described, was used in some measurements carried out at the *Fakultät für Elektrotechnik, Institut für Physik, Universität der Bundeswehr (München)*. This setup is also composed by a HP4156A precision semiconductor analyzer and a self-built <sup>4</sup>*He* bath cryostat. The main difference is that this setup does not implement Kelvin connections and a temperature sensor placed on the back side of the sample socked is provided. Measurements at different temperatures can then be carried out if the sample is not immersed into the liquid Helium bath, but held at some distance from the bath surface, and the sample temperature is monitored.

Early measurements were carried out using a fourth measurement setup, composed by an HP4145B (Yokogawa-Hewlet-Packard. Ltd. 1986) and a closed cycle Helium refrigerator. The refrigerator is constituted of a Helium compressor, a vacuum pump system and a test fixture where the samples, attached to gold plated ceramic dual in line packages, are mounted. This systems allows experiments to be carried out at temperatures down to 20 K. This experimental setup was used in the early phase of this research work, and no results obtained using this setup are published here. Nevertheless, the characteristics measured using this setup are in conformity with the data published in the following chapters.

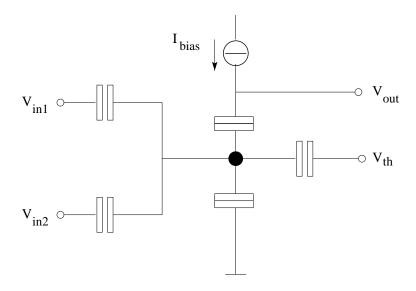

## 3.3 Experimental Setup for Measurements at Room Temperature

The measurements at room temperature were carried out using the HP4156A precision semi-conductor analyzer in connection with a HP 16058A test fixture. This test fixture is equipped with an electrostatic light-shielding cover. Triaxial cables were used to connect the HP 16058A to a HRSMU (High Resolution Source/Monitor Unit) channel of the HP4156A precision semi-conductor analyzer. As described above, all samples have been attached to ceramic dual in line packages (DIP) with gold plating and bonded using an ultra-sonic bonder with aluminum wiring. The minimum sampling time (minimum time interval between two successive measurement points) of the HP4156A is  $60\mu sec$ . and up to 10000 points can be acquired on a single sampling measurement (Yokogawa-Hewlet-Packard. Ltd. 1995).

This measurement setup was mainly used for the study of the random telegraph signal (RTS), discussed in chapter 6, and for sample characterization prior to cooling down.

# 4. Periodic Oscillations: Experimental Results

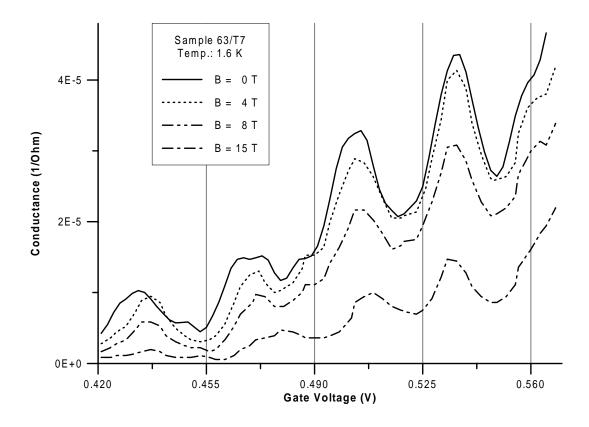

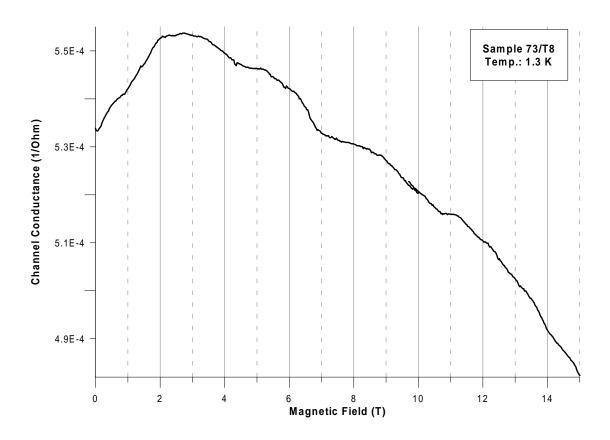

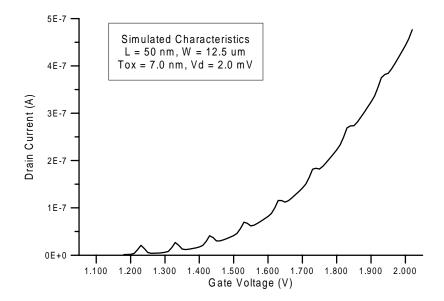

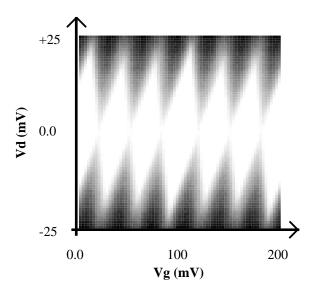

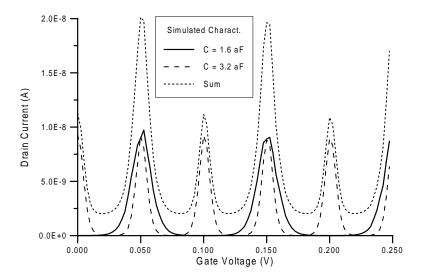

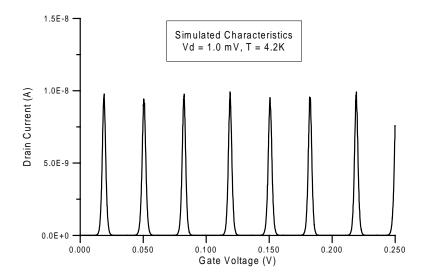

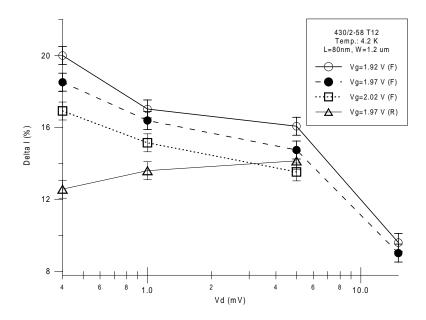

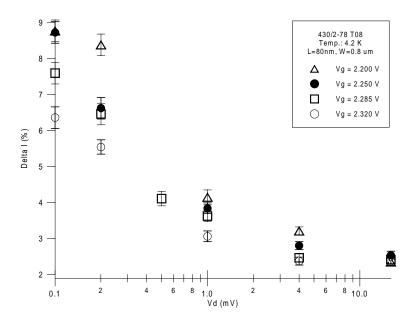

In this chapter the experimental investigation done to characterize the behavior of the sub-100nm MOSFETs at low temperature is described. In the measurements carried out at temperatures between 300 mK and 35 K unexpected periodic oscillations with negative differential resistance (NDR) are present in the  $I_D \times V_G$  characteristics. At room temperature the periodic oscillations can not be observed. Temperature and magnetic field dependence of sample characteristics are studied. Using the experimental setup described in chapter 3, magnetic fields up to B = 17 T could be applied.

Although similar behavior was already observed in silicon-on-insulator (SOI) devices (Peters, den Hartog, Dijkhuis, and Molenkamp 1998; Colinge, Baie, Bayot, and Grivei 1996), in MBE-grown vertical MOSFETs (Hansch, Rao, Fink, Kaesen, and Eisele 1998) and in GaAs FETs (Poole, Pepper, and Myron 1983), this is the first time that such phenomena is reported in a planar bulk MOS technology device.

#### **4.1** $I_D \times V_G$ Characteristics

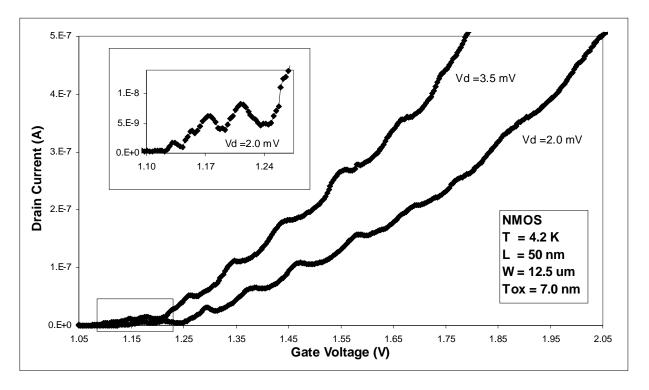

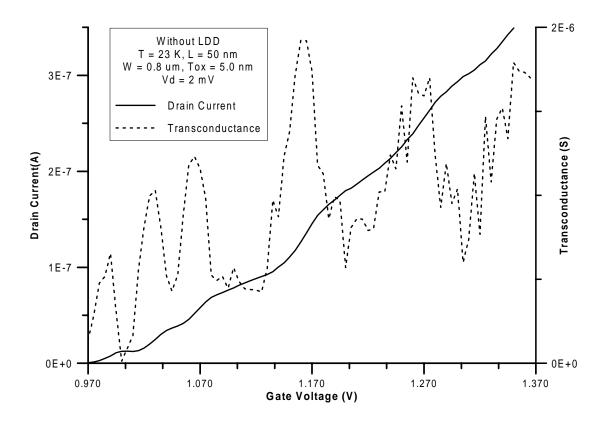

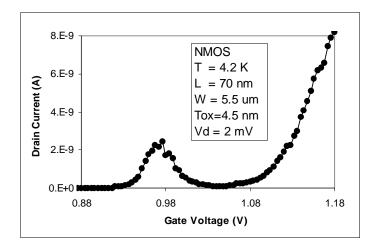

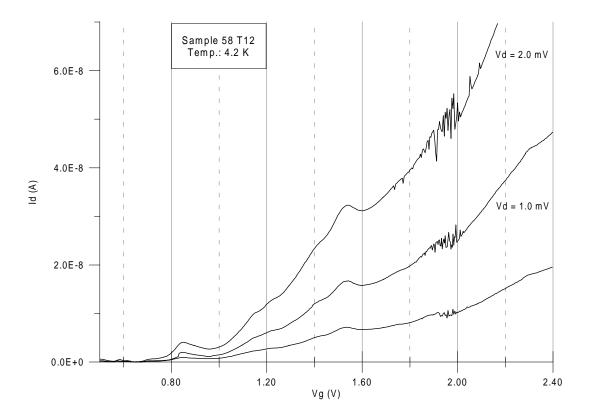

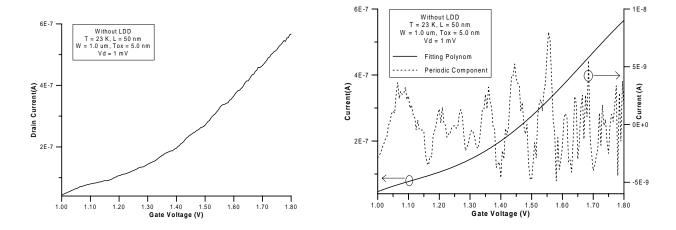

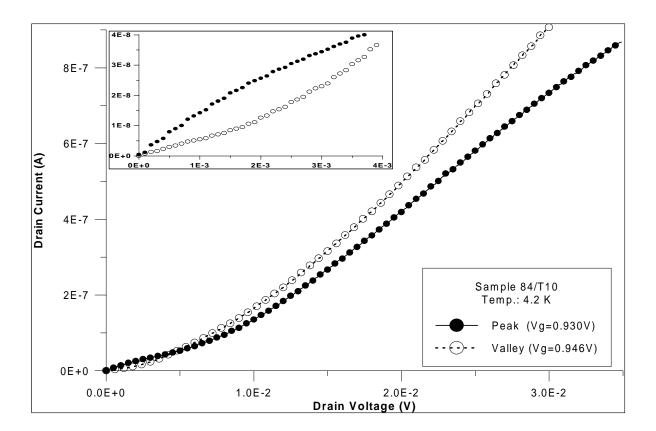

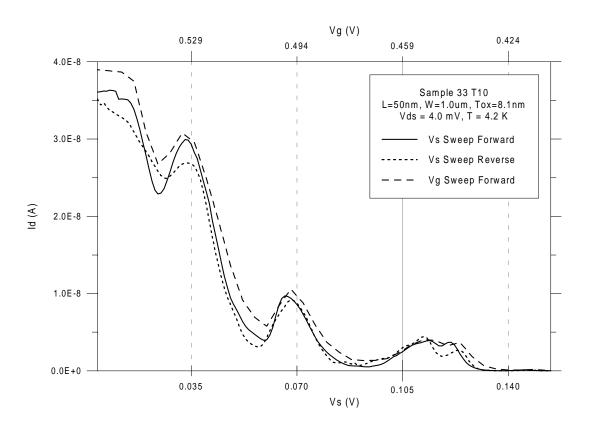

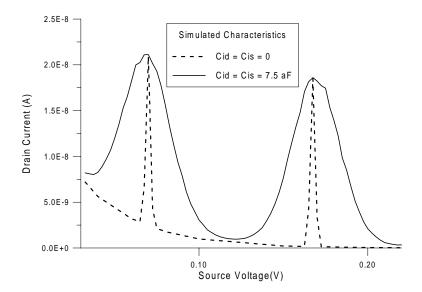

The typical  $I_D \times V_G$  (input) characteristics of sub-100nm MOSFETs at low temperature are depicted in Fig. 4.1, 4.2 and 4.3. As the gate leakage current is always below 10 pA, tunneling through the gate oxide can be neglected (Kunze, Drebinger, Klehn, and Lindolf 1994). The measured input characteristic shows unexpected periodic oscillations with negative differential resistance (NDR), similar to those found by the group of Eisele (Eisele, Baumgärtner, and Hansch 1995; Eisele, Baumgriner, and Hansch 1995; Hansch, Rao, Fink, Kaesen, and Eisele 1998) in vertical sub-100 nm MOSFETs grown by silicon molecular beam epitaxy. Although oscillations are always present, for devices with LDD as well as for devices without LDD, not all samples clearly show the periodicity observed in Fig. 4.1 to 4.3. This may be due to superposition of different physical phenomena involved in the electrical transport. Mesoscopic phenomena expected to play a role in the electrical transport of MOSFETs at cryogenic temperatures are discussed in chapter 5. Figure 4.5, for instance, depicts the characteristics of a sample for which transconductance fluctuations that are not periodic in  $V_G$  are present. In the higher  $V_G$  region (around 2 V) the fluctuations caused by the trapping and detrapping of electrons in localized defect states are also observed. This phenomenon is discussed in further detail in chapter 6.

Devices with effective channel lengths  $L_{eff}$  between  $\approx 28nm$  and  $\approx 120nm$  and channel widths W between  $0.6\mu m$  and  $100\mu m$ , processed on (100) silicon as described in chapter 3 are

**Figure 4.1:** Input characteristics of a nMOS transistor showing periodic oscillations. The inset depicts the subthreshold region in a more appropriate scale.

characterized. In the experimental data presented in this work, the effective channel length, estimated by means of process simulation with the two-dimensional process simulator DIOS (ISE - Integrated Systems Engineering AG 1994), is always given. For details on sample preparation and technology parameters, please refer to section 3.1.

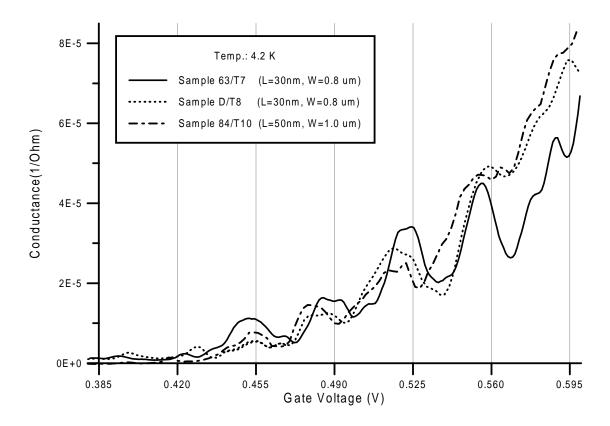

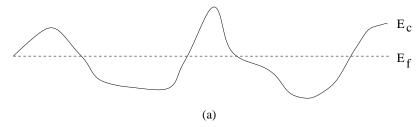

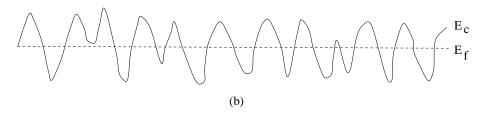

The oscillations are fairly reproducible from sample to sample and present from sub-threshold up to strong inversion. These characteristics, namely the presence of oscillation in strong inversion, is worth being emphasized. As discussed in chapter 2, at strong inversion screening of impurity and defect potentials is expected to be effective. No apparent relationship between the period of the oscillations and  $t_{ox}$ , W, L or channel doping concentration could be observed. For many samples the oscillation period in the region near the threshold voltage  $(V_T)$  is about 35 mV in gate voltage. These are followed by oscillations with a period of nearly 100 mV in the higher  $V_G$  region. The 35 mV period oscillations are better resolved for the L=30nm samples, as can be seen in Fig. 4.2. For these samples, the oscillations with a period of 100 mV in  $V_G$  are hard to be recognized at T > 4.2K. Samples with the shortest gate lengths show the strongest periodic oscillations, the same as observed by Poole et al. (Poole, Pepper, and Myron 1983) in GaAs FETs. From the 34 samples that did show periodic oscillations (Table 4.1) 22 have  $W < 2.5 \mu m$  and only 4 have  $W > 10\mu m$ . Up to now we were not able to find periodic transconductance fluctuations in devices with  $L_{eff} > 100nm$ . Transistor with micrometer channel lengths are also processed on the same wafer with the sub-100 nm MOSFETs. Eleven of these devices were characterized at low temperature. In contrast to the sub-100 nm MOSFETs, the input characteristics of these

**Figure 4.2:** Characteristics of three different samples showing oscillation near threshold. Curves are shifted in  $V_G$  for better comparison.

micrometer channel length devices do not show any marked structure. The  $I_D x V_G$  curve is much smoother, and a periodic component is not present at all.

No dependence of the oscillation period on temperature (Fig. 4.8), drain voltage or magnetic fields up to 17 T could be observed (discussed in section 4.4).

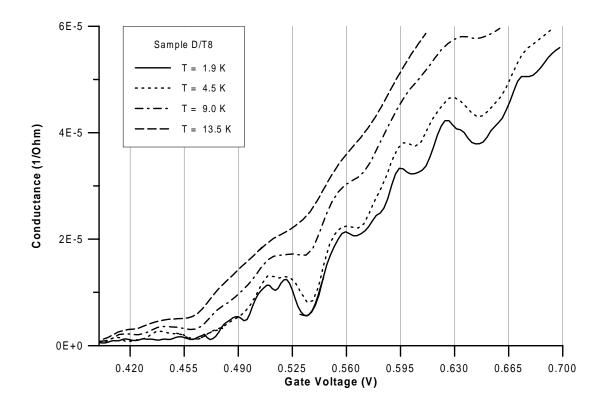

The periodic pattern smears out with rising temperature or increasing drain voltage, but can be found at temperatures up to 35 K and drain source electrical fields up to 2.4kV/cm, corresponding to a drain bias of 12mV for the L=50nm devices. On rising temperature, both peak and valley conductances do increase, as shown in Fig. 4.8. The valley current increases faster than the peak current, until the oscillations are smeared out. Different phenomena with distinct temperature dependency are present in channel current transport. Diverse parameters, as for instance the threshold voltage  $V_T$ , do have a strong temperature dependency. Therefore, it is difficult to isolate the current changes due to the temperature dependency of each phenomenon.

The oscillations are reproducible with temperature cycling. In fact, the conductance characteristics were studied over several months and remained essentially the same, even for samples that are cooled down to 4.2 K, brought back to room temperature and measured again at low tem-

perature in between time intervals as long as half a year. Nevertheless, the first transconductance peak always occurs in the subthreshold region of the transistor, as shown in Fig. 4.4.

**Figure 4.3:** Drain current  $I_D$  and transconductance  $g_m$  dependencies on gate voltage  $V_G$  in a device without LDD.

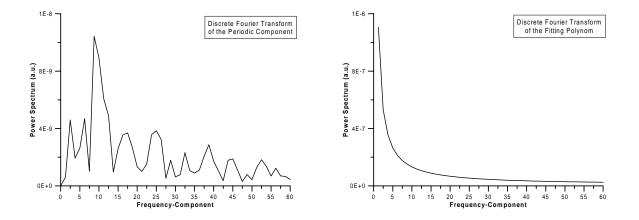

In order to make a quantitative analysis of the periodic components (power spectrum) present in the experimental data discrete Fourier transform was applied. The Fourier transforms were evaluated using the software package called *Mathematica* (Wolfram 1997; Wolfram 1996). In *Mathematica*, the discrete Fourier transform  $b_s$  of a data series  $a_r$  of length n is taken to be  $\frac{1}{\sqrt{n}}\sum_{r=1}^{n}a_re^{2\pi i(r-1)(s-1)/n}.$

The goal of this Fourier analysis was to bring about quantitative statements regarding the fraction of samples that show periodic oscillations. This can be done looking to the amplitude peaks found at the frequency components in the discrete Fourier transforms of the measured  $I_D$   $x V_G$  characteristics.

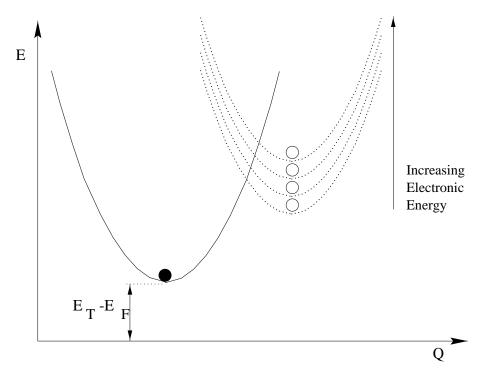

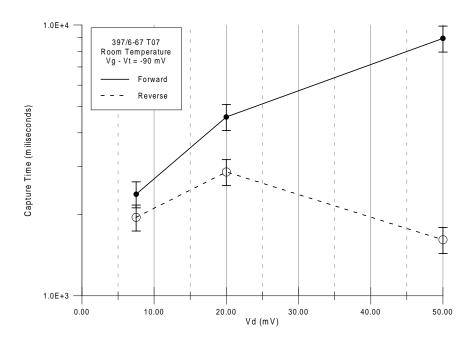

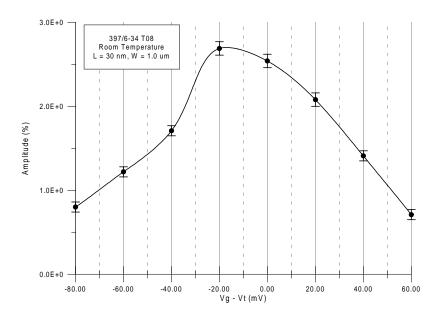

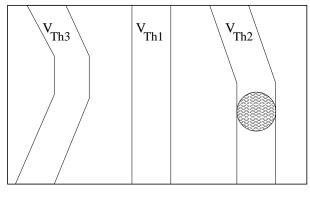

To perform Fourier analysis in an efficient way, the following methodology was automated using *Mathematica*: