### QcLab: A Framework for Query Compilation on Modern Hardware Platforms

#### Dissertation

zur Erlangung des Grades eines

Doktors der Ingenieurwissenschaften

der Technischen Universität Dortmund an der Fakultät für Informatik

von

Henning Funke

Dortmund

2022

25.03.2022

Tag der mündlichen Prüfung: Dekan/Dekanin: Prof. Dr.-Ing. Gernot Fink Gutachter/Gutachterinnen: Prof. Dr. Jens Teubner Prof. Dr. Thomas Neumann

#### **Abstract**

As modern in-memory database systems achieve higher and higher processing speeds, the performance of memory becomes an increasingly limiting factor. Although there has been significant progress, the bottleneck only has shifted. While earlier systems were optimized for *memory latencies*, current systems are rather affected by the limited *memory bandwidth*.

Query compilation is a proven technique to address bandwidth limitations. It translates queries via Just-In-Time compilation to native programs for the target hardware. The compiled queries execute with very high efficiency and only with a bare minimum of communication via memory. Despite these important improvements, the benefit of query compilation in certain scenarios is limited.

On the one hand query compilers typically use standard compiler technology with relatively long compilation times. Therefore the overall execution time can be prolonged by the additional compilation time. On the other hand, not all emerging database technology is compatible with the approach. Query compilation uses a tuple-at-a-time processing style that departs from the column-at-a-time or vector-at-a-time approaches that in-memory systems typically use. Especially data-parallel processing techniques, e.g. SIMD or coprocessing-techniques, are challenging to use in combination with the approach.

This work presents *QCLab*, a framework for query compilation on modern hardware platforms. The framework contains several new query compilation techniques that allow us to address the mentioned shortcomings and ultimately to extend the benefit of query compilation to new workloads and platforms. The techniques cover three aspects: *compilation*, *communication*, and *processing*. Together they serve as basis for building highly efficient query compilers. The techniques make efficient use of communication channels and of the large processing capacities of modern systems. They were designed for practical use and enable efficient processing, even when workload characteristics are challenging.

#### Contents

| Al | Abstract     |        |                                                  |    |  |

|----|--------------|--------|--------------------------------------------------|----|--|

| 1  | Introduction |        |                                                  |    |  |

|    | 1.1          | Query  | Translation and Execution                        | 2  |  |

|    | 1.2          |        | Challenges                                       | 5  |  |

|    | 1.3          |        | ibutions and Outline                             | 6  |  |

| 2  | Compilation  |        |                                                  |    |  |

|    | 2.1          | Introd | uction                                           | 10 |  |

|    |              | 2.1.1  | Intermediate Representation Levels               | 10 |  |

|    |              | 2.1.2  | Contributions                                    | 11 |  |

|    |              | 2.1.3  | Outline                                          | 12 |  |

|    | 2.2          | Query  | Translation                                      | 12 |  |

|    |              | 2.2.1  | Query Plan to IR                                 | 12 |  |

|    |              | 2.2.2  | IR to Machine Code                               | 14 |  |

|    |              | 2.2.3  | ReSQL Translation Mechanisms                     | 15 |  |

|    | 2.3          | Lightw | veight Abstractions                              | 17 |  |

|    |              | 2.3.1  | Virtual Registers                                | 17 |  |

|    |              | 2.3.2  | Function Calls                                   | 17 |  |

|    |              | 2.3.3  | Constant Loads                                   | 18 |  |

|    |              | 2.3.4  | Transparent High-Level Constructs                | 18 |  |

|    |              |        | ne Code Translation                              | 19 |  |

|    |              | 2.4.1  | Register Layout                                  | 19 |  |

|    |              | 2.4.2  | Translation Algorithm                            | 19 |  |

|    | 2.5          | Gettin | g More Out of Flounder                           | 24 |  |

|    |              | 2.5.1  | Utilizing Additional Database Knowledge          | 24 |  |

|    |              | 2.5.2  | Higher-Level IRs                                 | 25 |  |

|    | 2.6          | Evalua | C                                                | 25 |  |

|    |              | 2.6.1  | Compilation Times                                | 26 |  |

|    |              | 2.6.2  | Machine Code Quality                             | 28 |  |

|    |              | 2.6.3  | Post-Projection Optimizations                    | 29 |  |

|    |              | 2.6.4  | Overall Performance for Characteristic Workloads | 29 |  |

|    |              | 2.6.5  | Real World Performance                           | 31 |  |

|    | 2.7          |        | e Work                                           | 32 |  |

vi *CONTENTS*

|   |              | 2.7.1                         | Domain-Specific Processing              |  |  |  |  |  |

|---|--------------|-------------------------------|-----------------------------------------|--|--|--|--|--|

|   |              | 2.7.2                         | Hardware Architectures                  |  |  |  |  |  |

|   | 2.8          | Engin                         | eering Query Compilers                  |  |  |  |  |  |

|   | 2.9          | Summ                          | ary                                     |  |  |  |  |  |

| 3 | Con          | ımuni                         | cation 35                               |  |  |  |  |  |

|   | 3.1          | Introduction                  |                                         |  |  |  |  |  |

|   |              | 3.1.1                         | Contributions and Outline               |  |  |  |  |  |

|   | 3.2          | Macro                         | Execution Model                         |  |  |  |  |  |

|   |              | 3.2.1                         | Run-To-Finish (Not Scalable)            |  |  |  |  |  |

|   |              | 3.2.2                         | Kernel-At-A-Time                        |  |  |  |  |  |

|   |              | 3.2.3                         | Batch Processing                        |  |  |  |  |  |

|   | 3.3          | Micro                         | Execution Model                         |  |  |  |  |  |

|   |              | 3.3.1                         | Vector-At-A-Time                        |  |  |  |  |  |

|   |              | 3.3.2                         | Query Compilation                       |  |  |  |  |  |

|   | 3.4          | Data-I                        | Parallel Query Compilation              |  |  |  |  |  |

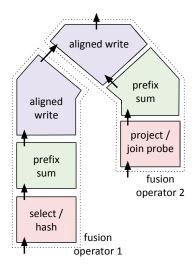

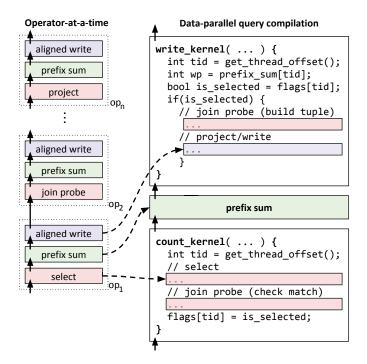

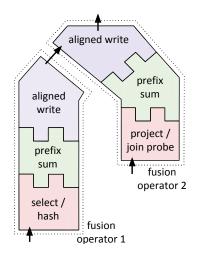

|   |              | 3.4.1                         | Fusion Operators                        |  |  |  |  |  |

|   |              | 3.4.2                         | Micro-Level Pipeline Layout             |  |  |  |  |  |

|   |              | 3.4.3                         | Instancing Relational Code Templates 45 |  |  |  |  |  |

|   |              | 3.4.4                         | Memory Access and Limitations           |  |  |  |  |  |

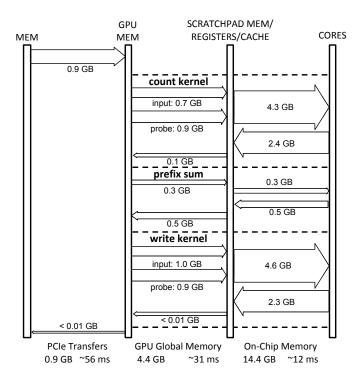

|   | 3.5          | Proces                        | ssing Pipelines in One Pass             |  |  |  |  |  |

|   |              | 3.5.1                         | Pipelining Data-Parallel Reductions 47  |  |  |  |  |  |

|   |              | 3.5.2                         | Code Generation for Compound Kernels 48 |  |  |  |  |  |

|   |              | 3.5.3                         | Memory Access and Limitations 50        |  |  |  |  |  |

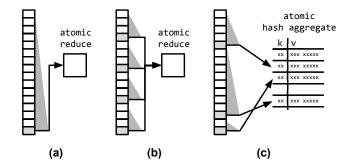

|   | 3.6          | Efficie                       | nt Pipelined Reductions                 |  |  |  |  |  |

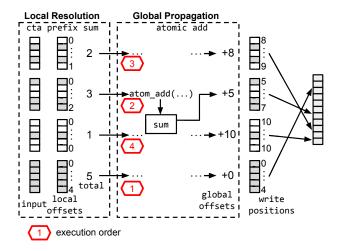

|   |              | 3.6.1                         | Local Resolution, Global Propagation 51 |  |  |  |  |  |

|   |              | 3.6.2                         | Local Resolution Mechanisms             |  |  |  |  |  |

|   | 3.7          | DBMS                          | Integration                             |  |  |  |  |  |

|   | 3.8          | 8                             |                                         |  |  |  |  |  |

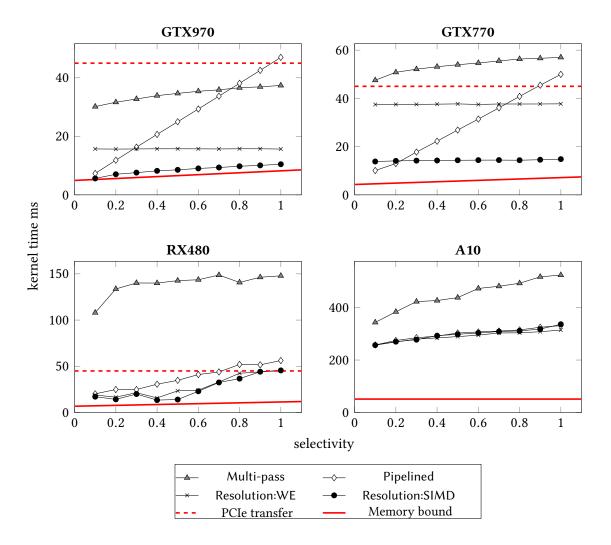

|   |              | 3.8.1                         | Pipelined Prefix Sum                    |  |  |  |  |  |

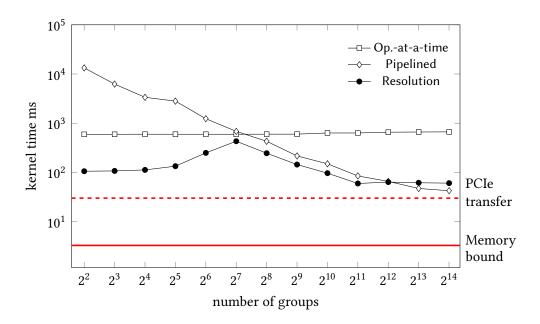

|   |              | 3.8.2                         | Pipelined Group By                      |  |  |  |  |  |

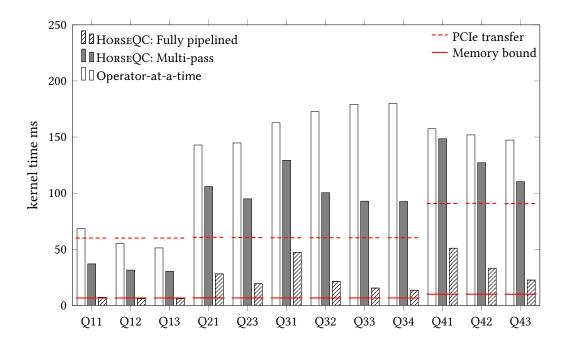

|   |              | 3.8.3                         | Star Schema Benchmark                   |  |  |  |  |  |

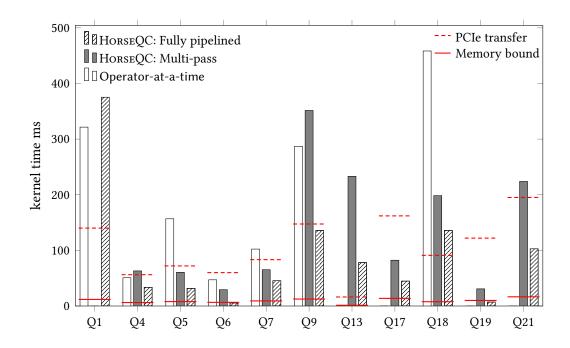

|   |              | 3.8.4                         | TPC-H Queries                           |  |  |  |  |  |

|   |              | 3.8.5                         | Scalability                             |  |  |  |  |  |

|   |              | 3.8.6                         | End-to-End Performance 61               |  |  |  |  |  |

|   | 3.9          | Discus                        | ssion                                   |  |  |  |  |  |

|   | 3.10         | More ?                        | Related Work                            |  |  |  |  |  |

|   | 3.11         | Engineering Query Compilers 6 |                                         |  |  |  |  |  |

|   | 3.12         | Summ                          | ary                                     |  |  |  |  |  |

| 4 | Processing 6 |                               |                                         |  |  |  |  |  |

|   | 4.1          | Introd                        | uction                                  |  |  |  |  |  |

|   |              | 4.1.1                         | State of the Art                        |  |  |  |  |  |

|   |              | 4.1.2                         | System: DogQC                           |  |  |  |  |  |

| CONTENTS | vii |

|----------|-----|

|          |     |

|                  |             | 4.1.3    | Contributions and Outline               | 68 |  |  |  |  |  |

|------------------|-------------|----------|-----------------------------------------|----|--|--|--|--|--|

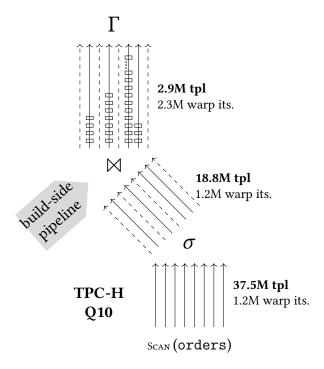

|                  | 4.2         | Non-U    | Uniform Pipelines                       | 68 |  |  |  |  |  |

|                  |             | 4.2.1    | Lane Activity                           | 69 |  |  |  |  |  |

|                  | 4.3         | ·        |                                         |    |  |  |  |  |  |

|                  |             | 4.3.1    | Poster Case 1                           | 69 |  |  |  |  |  |

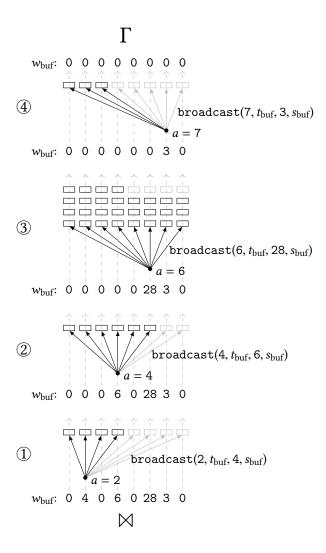

|                  |             | 4.3.2    | Push-down Parallelism                   | 71 |  |  |  |  |  |

|                  |             | 4.3.3    | Implementation                          | 72 |  |  |  |  |  |

|                  |             | 4.3.4    | Planning for Push-down Parallelism      | 74 |  |  |  |  |  |

|                  |             | 4.3.5    | Usage Scenarios                         | 74 |  |  |  |  |  |

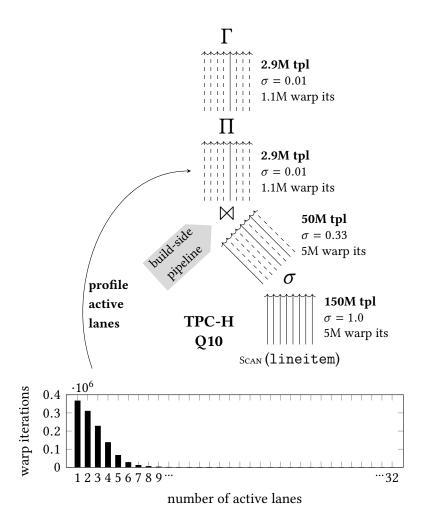

|                  | 4.4         | Filter I | Divergence                              | 75 |  |  |  |  |  |

|                  |             | 4.4.1    | Poster Case 2                           | 76 |  |  |  |  |  |

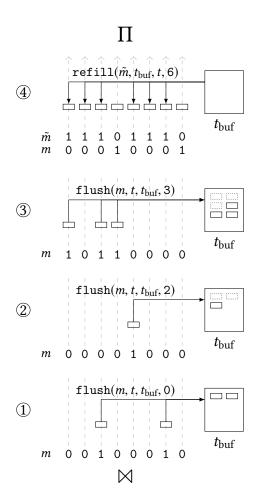

|                  |             | 4.4.2    | Lane Refill                             | 77 |  |  |  |  |  |

|                  |             | 4.4.3    | Implementation                          | 79 |  |  |  |  |  |

|                  |             | 4.4.4    | Planning for Lane Refill                | 80 |  |  |  |  |  |

|                  |             | 4.4.5    | Usage Scenarios                         | 81 |  |  |  |  |  |

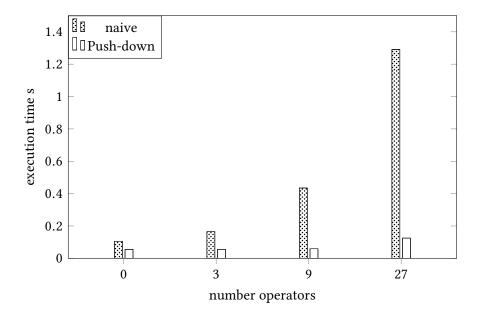

|                  | 4.5         | Evalua   | ation                                   | 82 |  |  |  |  |  |

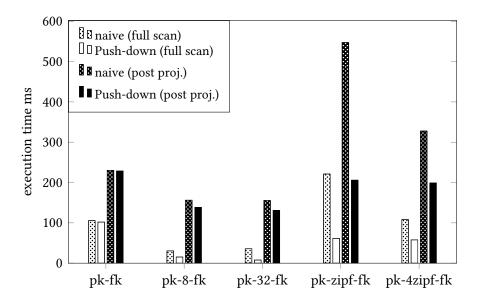

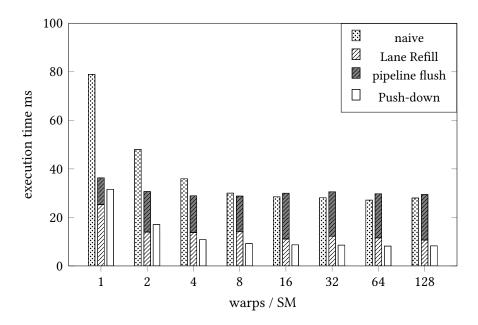

|                  |             | 4.5.1    | Effect of Push-down Parallelism         | 83 |  |  |  |  |  |

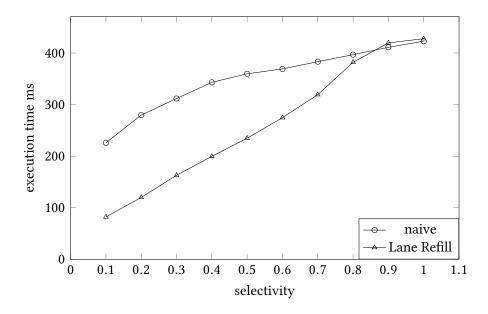

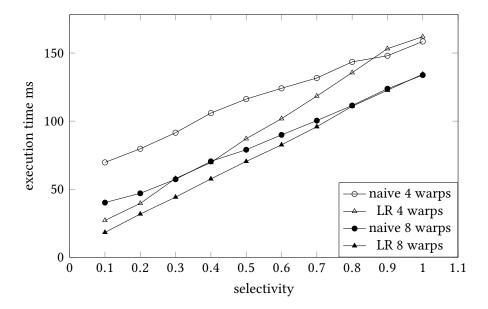

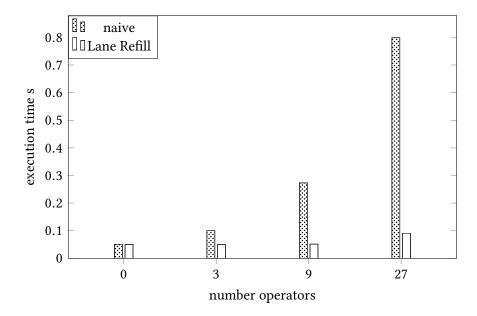

|                  |             | 4.5.2    | Effect of Lane Refill                   | 85 |  |  |  |  |  |

|                  |             | 4.5.3    | Push-down Parallelism vs. Lane Refill   | 88 |  |  |  |  |  |

|                  |             | 4.5.4    | Overall Performance                     | 89 |  |  |  |  |  |

|                  |             | 4.5.5    | Usage Scenario: String Pattern Matching | 93 |  |  |  |  |  |

|                  | 4.6         | More I   | Related Work                            | 93 |  |  |  |  |  |

|                  | 4.7         |          | eering Query Compilers                  | 94 |  |  |  |  |  |

|                  | 4.8         | Summa    | ary                                     | 95 |  |  |  |  |  |

| 5                | Conclusions |          |                                         |    |  |  |  |  |  |

|                  | 5.1         | Compi    | ilation vs. Interpretation              | 98 |  |  |  |  |  |

|                  | 5.2         |          | vare Platforms for Query Processing     | 99 |  |  |  |  |  |

|                  | 5.3         |          | t of the Covered Research               | 99 |  |  |  |  |  |

| Acknowledgements |             |          |                                         |    |  |  |  |  |  |

viii *CONTENTS*

# Introduction

Increasing main memory capacities have led to the development of *in-memory database systems*. Instead of using hard disk drives (*disks*) for storage, in-memory database systems keep their entire database in main memory. This approach has removed the disk access bottleneck, which previously was the strongest limiting factor for database processing. Systems that are optimized for in-memory processing, however, show a much greater potential [34]. In-memory technology has increased the relevance of database systems in existing [27] and new domains, e.g. data science [92]. A major benefit of such optimized systems are the high peformance gains that can be achieved.

An important factor for the performance of in-memory systems are *memory latencies* [15]. Memory latencies cause *memory stalls* when query execution waits for memory requests to be processed. In many cases the CPU caches help to reduce the number of memory stalls by providing cached data with shorter access times. Not all workloads, however, can benefit from the caches to a similar extent. Especially scan and hash-based techniques, that are typical for database workloads, have insufficient memory access locality for an effective use of the (relatively small) CPU caches. To address the impact of memory latencies, substantial research and development work has been performed by the database community. This work includes processing techniques for joins [15, 8], aggregation [68, 103], and projection [60]. The techniques typically increase the locality of data access, for instance with partitioning mechanisms, to achieve a more effective use of the CPU caches. Additional work leverages CPU prefetching features to *hide* memory latencies [23].

More recently another performance factor has gained importance. *Memory bandwidth* characterizes the data volume that can be serviced by memory over time. Workloads that are memory-intensive, such as database processing, are bounded in

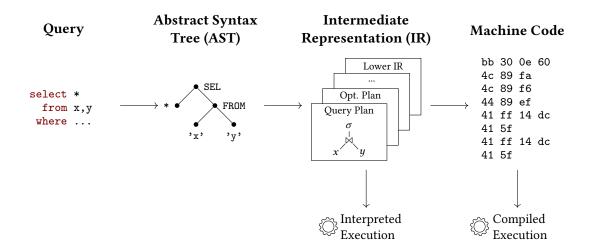

Figure 1.1: Translation and execution of a query by a database system.

throughput by the available bandwidth. Several techniques were proposed to reduce the bandwidth demand for database processing. Column-based technology [15] uses homogeneous data layouts to increase the efficiency of memory loads and stores. Vector-at-a-time processing [16] improves the cache-utilization for the communication between operations. However, technological improvements in hardand software enable processing speeds, that make it more and more challenging to provide sufficient bandwidth for the I/O operations during processing. While some technology exacerbates the issue (e.g. multi-core processors have limited per-core bandwidth), other may provide potential solutions (e.g. parallel coprocessors with high-bandwidth memory). This thesis deals with processing techniques that can be used to address bandwidth limitations during query processing. We take a look at different existing techniques and focus on query compilation as a promising approach.

#### 1.1 Query Translation and Execution

Queries are data processing tasks that run against the database to extract or to modify information. From a more general perspective, however, *a query is a program* and executing queries has many commonalities with executing other (general purpose) programs.

Figure 1.1 illustrates how database systems typically execute queries. The process resembles the way compilers work and a similar process (without the database specifics) is used by general purpose compilers, e.g. to compile C++ or Java programs. The query statement on the left is translated to a series of different representations to prepare it for execution (further on the right). The first step translates the query to the *abstract syntax tree* (AST). This step is performed by the parser. It applies the syntax rules of the SQL language to derive the query

statement from the language. The AST is the result of these rules and represents the *query syntax*. The query planner then maps the syntactic elements of the AST to relational operators (e.g. join  $\bowtie$ , selection  $\sigma$ ) that form the *query plan*. The query plan is a tree of relational operators that represents the *query semantics*.

The query plan is the first of several *intermediate representations* (IRs). Figure 1.1 shows the IRs with multiple layers that result from successive translation steps. After the query plan, several other IRs, e.g. the optimized query plan, follow. Each IR allows the compiler to use a well-suited representation when performing complex tasks such as resource allocation, optimization, or translation to a lower (machine-near) level.

After translation to the desired representation queries are executed. When an intermediate representation is used, queries are executed with *interpreted execution*. When machine code is used, queries are executed with *compiled execution*. In the following we discuss the implications of both modes.

**Interpreted Execution** Traditionally database systems have used interpreted execution, e.g. Volcano [36], to execute queries. The *interpreter* takes an intermediate representation of the query and executes its elements step by step. For instance, it traverses the query plan's operators and for each traversal step, it executes the operator's implementation. Some systems, e.g. PostgreSQL [93], interpret the query plan directly. Other systems, e.g. MonetDB [15] or SQLite3 [91], translate the query plan to an imperative IR with *commands* and execute those. For simplicity we call all executed IR elements commands. Commands may (and typically will) read tables from the database, e.g. when executing scan operators. The rows resulting from interpretation of the IR form the query result.

Interpreted execution includes an additional cost for performing the interpretation itself. Every command that is executed has to be *decoded* first. During decoding the interpreter reads a command and jumps to the code location with its implementation. To perform this decoding work, the CPU executes additional instructions that add to the workload of operator processing. For in-memory techniques, where disk access no longer dominates execution times, this quickly becomes a limiting factor. Especially interpretation techniques that perform decoding for every row of a table are strongly affected. The accumulating interpretation work can dwarf the actual processing work and has been identified as *interpretation overhead* [16].

**Compiled Execution** Query compilation is a processing technique that solves the problem of interpretation overheads. As illustrated on the right-hand side of Figure 1.1, the approach takes query translation one step further and translates queries to machine code before their execution. This enables highly efficient query processing and makes the approach very attractive for addressing the performance demands of modern in-memory systems. At the same time, database systems are compilers anyhow and are therefore well suited for applying compilation techniques. For these reasons, we make query compilation the focus of this work

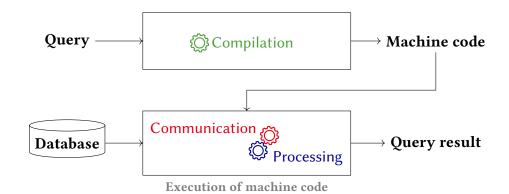

Figure 1.2: Illustration of compiled query execution. Three central concepts that are addressed in this thesis are visualized with gear symbols.

in the following we present three concepts with a central role.

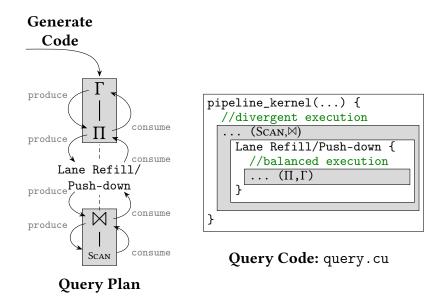

Compiled query execution is illustrated in Figure 1.2. The figure shows three central concepts with gear symbols. The top part of the figure illustrates *compilation*, the bottom part *execution*. In the top part © Compilation performs translation of the query to a machine code representation, the *compiled query*. This translation is a form of Just-In-Time (JIT) compilation because queries are compiled immediately when the database is queried. It therefore relies on short compile times. To perform compilation, database systems translate the query plan (or other representations of the query) to a low-level IR, e.g. LLVM IR [55], which supports translation to machine code. The IR library is then used to translate the IR to the compiled query, which is executed afterwards.

Query execution (Figure 1.2, bottom) is initiated by pointing the CPU to the compiled query (e.g. with a function call). The CPU proceeds with execution of the compiled query. During execution Processing concerns the execution of relational operators. The operators of the query are stringed together in the machine code and are therefore executed by the CPU coherently. There is no decoding work required as the CPU steps from operator to operator without interventions being necessary. This makes processing very efficient and removes the interpretation overhead entirely. **OCCOMMUNICATION** Services processing. This is illustrated by the engaging gears (Figure 1.2, bottom). It provides data access and data passing methods that are used for sharing data between operators and for accessing relations. By compiling several relational operators to the same binary function, query compilation has the opportunity for a very efficient way of sharing data between operators. The operators can share data simply by accessing the same CPU registers. This enables highly efficient use of memory bandwidth and improves the communication speed over techniques that materialize tuples in memory or in caches.

Through the compilation to machine code, compiled execution has the potential to reach *optimal* execution performance. To reach this optimum, however, a costly

compilation process would be required to determine the corresponding machine code representation. The two goals of low execution times and low compilation oppose each other in the goal for overall short response times. A good solution for this tradeoff is an important design decision for query compilers and can also depend on workload characteristics. The techniques presented in this work address different aspects of this tradeoff and represent new solutions for challenging workloads.

#### 1.2 Open Challenges

We discuss several open challenges for query compilation in relation to the previously introduced concepts. Some of the open challenges result from the mismatch between interpretation-based database technology and compiled query exeution. Other challenges stem from requirement differences between query compilers and classical compilers.

**Compilation** During compilation, compilers go through several translation steps and yield an intermediate representation (IR) of the program. The IRs help compilers to handle translation complexity and to apply optimizations. Query compilers have used existing compiler infrastructure for intermediate representations. However, the generality of such solutions limits their benefit. Queries have a simpler and more well-defined form than general purpose programs and may therefore be translated with less effort. Query processing represents new incentives and opportunities for the development of compiler techniques that are specifically made for database workloads.

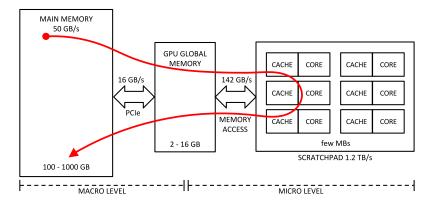

**Communication** During query processing data moves from their storage locations into processing units and back. For these communication processes different hardware channels, e.g. bus links and main-memory access, with varying transfer speeds are used. Especially for coprocessor systems this can become a strong limiting factor as they rely on additional communication channels during computations. The issue is amplified by processing techniques that perform multiple passes over the input, which are typical on massively parallel processing devices.

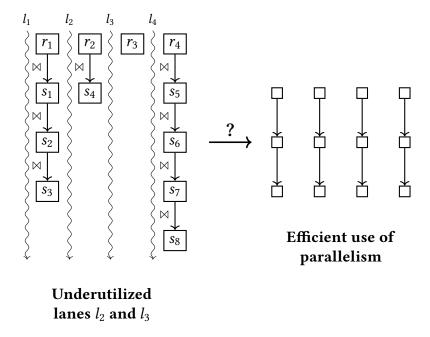

**Processing** Data-parallel processing devices handle multiple elements simultaneously. This increases the processing capacity to an otherwise impossible extent. The performance gains can be high, especially for massively parallel processing units that handle thousands of tasks simultaneously. However, to achieve the desired benefit, an effective distribution of work is essential. Otherwise processing units may run empty while others operate. Especially with processors that support fine-grained parallelism, such as those supporting multi-element instructions, handling these asymmetries is a challenge.

#### 1.3 Contributions and Outline

This thesis focuses on query compilers for modern hardware platforms. We present a number of analyses and techniques that address the previously motivated open challenges. The contributions and correspondingly the chapters of this thesis are structured according to the three components *compilation* (Chapter 2), *communication* (Chapter 3), and *processing* (Chapter 4). Together the presented techniques provide the basis for building highly efficient query compilers.

The thesis starts in Chapter 2 with a compilation technique that is designed for database workloads. The technique was first introduced in

[29] H. Funke, J. Mühlig, and J. Teubner. Efficient generation of machine code for query compilers. In *DaMoN workshop*, pages 1–7, 2020

and includes a new intermediate representation that enables tailoring of the machine code generation steps used by query compilers to the demands database workloads. We show that this simplifies the compilation process to the benefit of low JIT-compilation times. A follow-up publication

[33] H. Funke and J. Teubner. Low-Latency Compilation of SQL Queries to Machine Code. *PVLDB*, 14(12):2691–2694, 2021.

showcases the compilation of SQL statements to machine code in a more comprehensive setting. We use this as basis for an in-depth evaluation of compilation and execution performance. Finally

[30] H. Funke, J. Mühlig, and J. Teubner. Low latency query compilation. *The VLDB Journal*, 2022

extends the compilation approach to additional use cases and shows how it can be used in a comprehensive system.

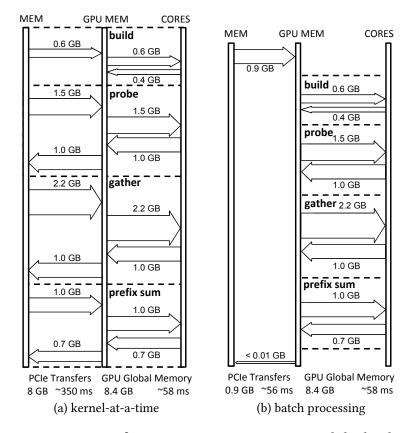

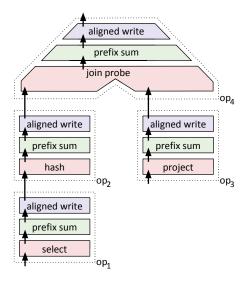

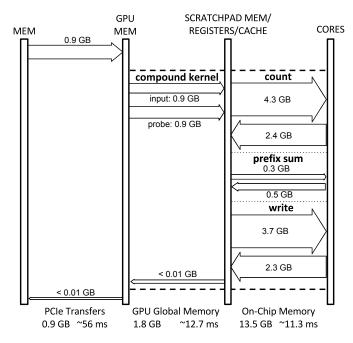

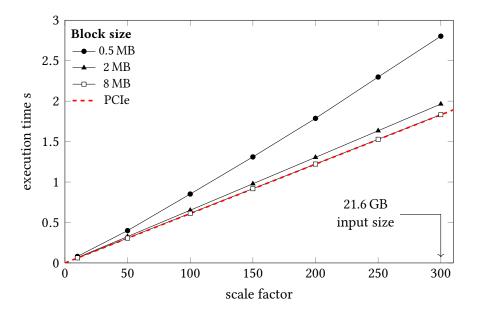

Chapter 3 contains a thorough analysis of the communication behavior of coprocessor systems during query execution. We show that existing processing techniques are affected by bandwidth limitations on multiple levels and that compilation techniques can help to alleviate them. However, massively parallel coprocessors typically use processing techniques with multiple passes over the input. We introduce a new technique that was published along with the communication analysis in

[28] H. Funke, S. Breß, S. Noll, V. Markl, and J. Teubner. Pipelined Query Processing in Coprocessor Environments. In *SIGMOD*, pages 1603–1618. ACM, 2018.

The technique only uses a single pass over the input relations and we show experimentally that this leads to a distinct reduction of the bandwidth demand to the benefit of efficient communication.

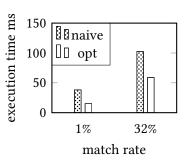

Chapter 4 addresses the problem of imbalances during compiled execution on data-parallel architectures. We present two balancing techniques that integrate with the single-pass processing approach [28]. The techniques restore processing efficiency when imbalances otherwise leave processing units unused. This enables effective use of the large processing capacities of parallel coprocessors even for workoads that are challenging to parallelize. The techniques were published in

[31] H. Funke and J. Teubner. Data-parallel query processing on non-uniform data. *PVLDB*, 13(6):884–897, 2020

and the follow-up publication

[32] H. Funke and J. Teubner. Like water and oil: with a proper emulsifier, query compilation and data parallelism will mix well. *PVLDB*, 13(12):2849–2852, 2020

presents a monitoring tool that helps to better understand the balancing effects. We conclude the chapter with an experimental analysis that shows the high processing speeds that can be achieved with our techniques. Finally Chapter 5 wraps up the thesis. In the development of our techniques, we emphasized the practical feasibility and built several prototype systems. To leverage the insight from these projects, we add a discussion on the engineering aspects in each chapter.

**Additional Work** During the writing and prior, the author contributed to other publications that are not part of this thesis. This work includes the following:

- [18] S. Breß, H. Funke, and J. Teubner. Robust query processing in co-processor-accelerated databases. In *SIGMOD*, pages 1891–1906. ACM, 2016.

- [19] S. Breß, B. Köcher, H. Funke, S. Zeuch, T. Rabl, and V. Markl. Generating custom code for efficient query execution on heterogeneous processors. *The VLDB Journal*, 27(6):797–822, 2018.

- [70] S. Noll, H. Funke, and J. Teubner. Energy efficiency in main-memory databases. *Datenbank-Spektrum*, 17(3):223–232, 2017.

The Author's Contributions According to §10 (2) of the doctoral regulations of the computer science dapartment at TU Dortmund University from August 29, 2011, the author should indicate their own contributions to the results of collaborations that are used. The author is principal author of the articles [28, 29, 31, 32, 33] and of all contents from the articles that are used in chapters of this thesis. He is responsible for the concepts, the implementations, the presentation, and the analyses.

## 2 Compilation

By compiling queries to machine code, query compilation enables very high processing speeds and reduces the bandwidth demands during processing to a bare minimum. This makes the technique very attractive for modern in-memory systems. The technique, however, introduces *compilation* as an additional step to query processing. This causes a compilation overhead that adds to the response times of queries. The overhead is relatively high for queries with a short execution time and for queries with high complexity.

This chapter introduces *Flounder IR*, a new lightweight intermediate representation for query compilation to address the problem of compilation overheads. *Flounder IR* is close to machine assembly and adds just that set of features that is necessary for efficient query compilation: virtual registers and function calls ease the construction of the compiler front-end; database-specific extensions enable efficient pipelining in query plans; more elaborate IR features are intentionally left out to maximize compilation speed.

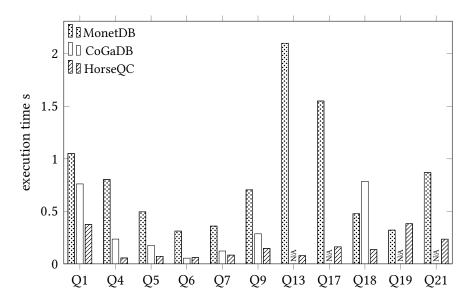

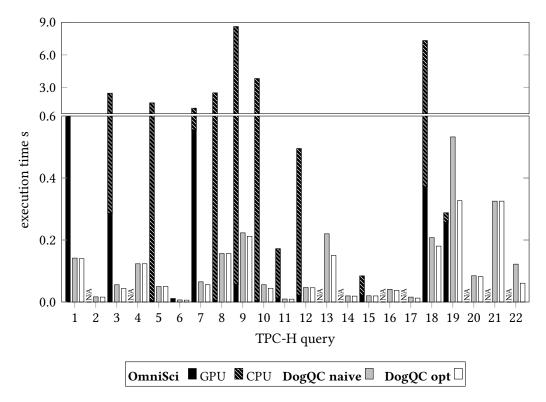

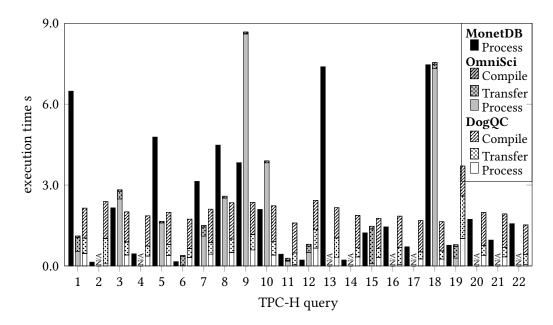

We present and motivate *Flounder IR* and showcase its capabilities with the prototype system *ReSQL* that uses the IR for compilation. *ReSQL* employs similar compilation techniques as existing query compilers, but leverages the capabilities of *Flounder IR* and the *Flounder* library to achieve low compilation times. We demonstrate with micro-benchmarks and for real world workloads that our approach significantly reduces query compilation times. We show reductions in compilation times up to two orders of magnitude over LLVM and show improvements in overall execution time for TPC-H queries up to 5.5× over state-of-the-art systems.

Parts of this chapter are contained in published articles [29, 33, 30].

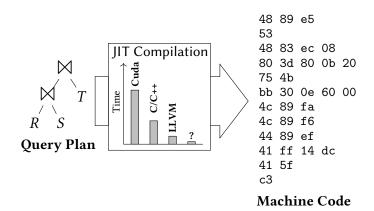

Figure 2.1: Effect of different intermediate representation levels on JIT query processing performance.

#### 2.1 Introduction

Query compilation is a technique for query execution with extremely high efficiency. It uses *just-in-time* (JIT) compilation to generate custom machine code for the execution of every query. The approach leverages a compiler stack that first translates the query from a relational query plan to an *intermediate representation* (IR), and then from the IR to *native machine code* for the target machine. The execution-efficiency of the compiled code is very high compared to standard interpretation-based backends. However, by using compilation the technique adds a step to query execution, which introduces translation cost. Especially short-running queries and queries with high complexity experience a relatively high translation cost, which ultimately extends query response times.

When using query compilation for queries on smaller datasets, the relative cost of compilation increases. The query engine spends most of its time on compilation before entering execution only for a very short time. Further, complex queries can have particularly long compilation times due to complexity of algorithms used in JIT machine code translation [80]. Approaches to mitigate the impact of compilation time on response time have been proposed previously [53]. However, these typically rely on *both* an interpretation-based and a compilation-based backend at a high implementation cost.

#### 2.1.1 Intermediate Representation Levels

The intermediate representation is an important design choice for query compilers. Figure 2.1 illustrates the effect of the IR choice on JIT compile times. Query compilers with high-level IRs, such as C/C++ [51, 89, 25] or OpenCL and Cuda [19, 31, 28, 79] generally have longer compilation times than query compilers that generate lower-level IRs such as LLVM IR [69, 74]. Existing work on JIT compilers,

11

however, shows the feasibility of much shorter compile times [6, 4] than those of LLVM. In fact non-database JIT compilers reach break-even points for dynamic compilation versus static compilation already for thousands of records [6]. By contrast, state-of-the-art LLVM-based query compilers have compilation times of tens of milliseconds [69], which is sufficient time to process queries on millions of tuples [16]. This raises the question illustrated by the bar '?' in Figure 2.1: How can such short compilation times be adopted for database systems that perform query compilation?

LLVM IR is general purpose and was designed to serve as backend for the translation of high-level language features [55]. Being general purpose, LLVM is relatively heavyweight and devises a translation stack that is "overkill" for relational workloads. The code for relational queries typically consists of tight loops with conditional code mainly to drop non-qualifying tuples. This plain structure offers potential for much simpler translation techniques than those used by general purpose translators, which leverage complex code analysis and register allocation algorithms.

#### 2.1.2 Contributions

In this work, we present the intermediate representation *Flounder IR* and the *ReSQL* database system, which represent our new approach to query compilation with low compilation latencies.

**Flounder IR** We propose Flounder IR as a lightweight domain-specific IR that is designed for fast compilation of database workloads. Flounder IR is based on machine assembly and adds several features for efficient use by query compilers: virtual registers enable efficient handling of attribute data; function calls allow interfacing with the database library; database-specific register allocation enables efficient pipelining. The IR features are designed to be lightweight and we avoid the use of more elaborate features to allow for fast translation. Along with the IR, we show the techniques for translation of Flounder IR to machine code used by the Flounder library.

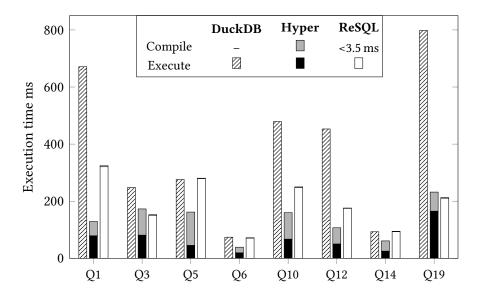

**ReSQL** The ReSQL database system was developed as a showcase for low-latency query compilation with Flounder IR. ReSQL provides a full translation stack from SQL to machine code and supports a variety of queries. We discuss the interaction of ReSQL's translation components with Flounder IR and use the system to perform an experimental evaluation on TPC-H benchmark [13] workloads. The analysis shows that our query compilation approach reduces compilation times while preserving high processing speeds. We show with speedups up to 5.5× over a state-of-the-art LLVM-based query compiler, Hyper, that our approach achieves better tradeoffs between compilation and execution time.

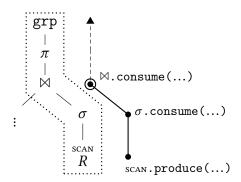

Figure 2.2: Translation of the probe-side pipeline of a query plan.

#### **2.1.3** Outline

This chapter is structured as follows: The next Section 2.2, illustrates how query compilers use Flounder IR for query translation. Section 2.3 then details the design of Flounder IR. Section 2.4 shows the translation of Flounder IR to machine code. Section 2.5 discusses further improvements and applications of our approach. Section 2.6 evaluates the approach experimentally and Section 2.7 discusses future work. In Section 2.8, we discuss the engineering aspects of the techniques and finally Section 2.9 wraps-up the chapter with a summary.

#### 2.2 Query Translation

Query compilation typically involves one step that translates relational queries to an *intermediate representation* (IR) and another step that translates the IR to machine code. In the following, we give an overview of how both steps are realized for query compilation with our intermediate representation Flounder IR.

#### 2.2.1 Query Plan to IR

The first translation step traverses the query plan and builds an intermediate representation of the query functionality. A common way to do this is the produce/consume model [69], which emits code for operator functionality either in produce or consume methods. We call these methods *operator emitters*. Figure 2.2 illustrates the operator emitters that are executed during translation of a sample query. The *build pipeline* on the left of the join populates the join hash table. It was translated previously. The *probe pipeline*, surrounded by the dotted line, accesses the join hash table. We look at its translation in detail.

The code to scan R was already emitted by scan.produce(...). It contains a loop that iterates over the table R and reads its tuples. The code for selection was emitted by  $\sigma.consume(...)$  and now the hash join follows with  $\bowtie.consume(...)$ . The implementation of the method is shown in Figure 2.3, which uses a notation

#### Translate Hash Join Operator to IR

```

Function ⋈.consume(attributes, caller):

if caller is ⋈.left:

/* build-side */

ht \leftarrow createHashtable(...)

emit entry \leftarrow ht_ins(ht, \bowtie.buildKey)

/* get bucket */

3

emit materialize (entry, attributes)

/* write to ht */

a_1 \leftarrow attributes

if caller is ⋈.right:

/* probe-side */

6

emit entry \leftarrow null

/* initialize */

emit while (true):

/* loop over join matches */

/* probe hash table to get next matching entry */

emit entry \leftarrow ht_get(ht, \bowtie.probeKey, entry)

emit if entry is null:

/* check result */

10

emit break

/* no more match */

emit dematerialize (entry, a_l)

/* read to regs */

12

\bowtie.parent.consume (a_1 \cup attributes, \bowtie)

/* next ops */

13

```

Figure 2.3: Operator emitter of the hash join operator. We underlined the functionality that is placed in the JIT query.

similar to Kersten et al. [49]. Code lines following an **emit** statement are underlined to emphasize that this code is not executed immediately but instead placed in the JIT query. For instance createHashtable(..) is not underlined (line 2) and is therefore executed during translation. By contrast ht\_ins(..) is underlined (line 3) and is therefore placed in the compiled code. This leads to repeated execution of the line for every tuple of the scanned table.

In the example ⋈.consume(...) is called from its right child and therefore the probe-side code is produced (lines 7–13). The code first initializes the variable *entry*, which holds hash probe results (line 7) and then loops over the hash join matches (lines 8–13). In the loop, we first call ht\_get(...) to retrieve the next match (line 9) and then perform a check to exit when no more matches exist (lines 10–11). To process *join matches*, we read the attributes of the match to registers (line 12) and then the join's parent operators place their code by calling consume(...) (line 13).

The resulting intermediate representation is shown in Figure 2.4 (a)<sup>1</sup>. It performs the described probe functionality. We briefly describe the resulting IR here and provide a detailed description of the used Flounder IR features in Section 2.3.

The attribute values are held in  $\{r_a\}$ ,  $\{s_a\}$ , and  $\{s_b\}$  and the locations of hash table entries in  $\{entry\}$ . The hash\_get(...) call is realized with mcall and the loop over the probe matches with a combination of compare (cmp) and two

$<sup>^{1}</sup>$ We use an nasm-style assembler notation with destination operand on the left and source operand on the right.

```

[...] ; child code

[...] ; child code

mov r11, 0; init entry

vreg {entry}

loop_headN: ;while head

mov {entry}, 0

mov

[rsp-8], r8; caller-

[rsp-16], r9 ;save

;while head

mov

loop_headN:

mov

[rsp-24], r10

mov rdi, 0x25cac0 ;call

;ht_get(..) call

mcall {entry},{ht_get},

mov rsi, r9

;params

{ht},{r_a},{entry}

mov

rdx, r11

rsp, 24 ;adjust stack

;break when entry=NULL

sub

cmp {entry}, 0

mov

rax, 0x42fa10

je loop_footN

call rax ;ht_get call

;dematerialize ht entry

add rsp, 24 ;restore stack

vreg {s_a}

mov r8,

[rsp-8] ;restore

vreg {s_b}

mov r9,

[rsp-16] ;caller-

mov {s_a}, [{entry}]

mov r10, [rsp-24] ;save

mov {s_b}, [{entry}+8]

mov r11, rax ;return value

[...] ;parent.consume(..)

cmp r11, 0 ; break condition

loop_footN

clear {s_a}

je

;demate-

clear {s_b}

mov r12, [r11]

;loop foot

mov r13, [r11+8] ; rialize

jmp loop_headN

[...] ;parent.consume(..)

loop_footN:

jmp loop_headN ;next probe

clear {entry}

loop_footN:

[...] ; child code

[...] ; child code

Flounder IR

x86_64 assembly

(in-memory)

(in-memory)

(a)

(b)

```

Figure 2.4: Intermediate representation of hash join probe functionality (a) and corresponding machine assembly (b).

jumps (jmp, je). To read attributes from a hash table entry (dematerialize), we use mov from a memory location in brackets [] to e.g. {s\_a}.

#### 2.2.2 IR to Machine Code

The next step translates the query's intermediate representation to machine code. The machine code needs to follow the application binary interface (ABI) of the execution platform. In this work, we use the target architecture x86\_64 [61].

The Flounder IR emitted by the hash join is translated to the machine assembly shown in Figure 2.4 (b). Several abstractions that were used during IR generation are now replaced by machine-level concepts. E.g. the machine assembly uses processor registers such as r12 instead of {s\_a}. Further, the machine assembly uses additional mov instructions to transfer values between registers and the stack, e.g. mov r8, [rsp-8]. The translation process from Flounder IR to machine code needs to manage machine resources such as registers and stack memory and find

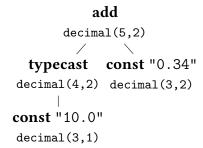

Figure 2.5: Typed expression tree for the expression 10.0 + 0.34.

an efficient way for their use during JIT query execution.

#### 2.2.3 ReSQL Translation Mechanisms

For a more comprehensive picture, we present two more essential translation mechanisms that are used for the translation of queries to Flounder IR by ReSQL. We first discuss the translation of scalar expressions, which are used in SQL statements, e.g. for selection or join criteria. Then we discuss handling of tuples in the implementation of operator emitters.

**Expression Translation** To illustrate expression translation, we use the expression 10.0 + 0.34, a sum of two decimal constants, as example. ReSQL uses 64 bit integers for decimal arithmetics and thus represents the values as 100 and 34 along with the *base* and *precision*. The precision is the number of digits in total and base is the number of digits following the decimal point.

For JIT-based evaluation, the expression translator performs two steps. The first step is type resolution, a standard procedure that derives the result type of each expression node. The leaf types decimal(3,1) and decimal(3,2) are given by the constants. The expression translator applies type rules to derive the typed expression tree shown in Figure 2.5. One typecast was inserted to maintain the same base for the add. Then the second step emits Flounder IR for the expression tree. Starting with the leaf expressions, code for the evaluation of each node is emitted. The resulting Flounder IR to evaluate the expression is shown in Figure 2.6. The code uses, e.g. vreg {x} and clear {x} to indicate the validity range of {x}. First both constants are loaded. Then the typecast for {dec\_const1} is evaluated by multiplying with 10. Finally the add is evaluated and the result is stored in {add\_res0}. The IR-code is inserted into the code frame of the query and translated to machine code along with the query.

**Handling of Tuples** In JIT-based execution, the individual values of a tuple are distributed across registers. For the implementation of operator emitters, however, it is still useful to handle tuples as a single entity [49]. ReSQL provides several

```

;const "0.34"

vreg {dec_const0}

mov {dec_const0}, 34

;const "10.0"

vreg {dec_const1}

{dec_const1}, 100

;typecast [decimal(3,1) to decimal(4.2)]

vreg {cast_res0}

{cast_res0},

{dec_const1}

mov

clear {dec_const1}

imul {cast_res0}, 10

;add

vreg {add_res0}

mov

{add_res0},

{dec_const0}

clear {dec_const0}

add {add_res0},

clear {cast_res0}

{cast_res0}

;[...] work with add_res0

clear {add_res0}

```

Figure 2.6: Flounder IR produced for the expression 10.0 + 0.34.

```

tup = Values::evaluate(expr);

Evaluate the list of expressions expr.

tup = Values::dematerialize(loc, schm);

Scan a tuple with schema schm from location loc.

hash = Values::hash (tup);

Hash the tuple tup.

flag = Values::checkEquality(tup1, tup2);

Check tuples tup1 and tup2 for equality.

Values::materialize(tup, loc);

Write tuple tup to location loc.

```

Figure 2.7: Tuple-based code generation methods allow us to handle lists of attribute registers as if they were coherent tuples.

code generation functions in the Values namespace for this purpose. These are shown in Figure 2.7. To evaluate the projection expressions from a select-clause, for example, we use tup=Values::evaluate(projs). The result tup is a list of virtual registers that hold the expression results, ultimately a tuple. Similarly, lists of virtual registers are used to hold tuples after scanning them or when applying a hash function.

#### 2.3 Lightweight Abstractions

Flounder IR is similar to x86\_64 assembly, but it adds several *lightweight abstractions*. The abstractions are designed with the interface to the query compiler *and* with the resulting machine code in mind. In this way, Flounder IR passes just the right set of information into the compilation process. For operator emitters, the IR provides independence of machine-level concepts, which allows similar code generation as is typically performed with LLVM. For translation to machine code, the abstractions are sufficiently lightweight to avoid the use of compute-intensive algorithms. Additionally, the IR contains information about the relational workload that enables efficient tuning of the machine code.

In the following, we present the lightweight abstractions. They add several pseudo-instructions, i.e. vreg, clear, and mcall to x86\_64 assembly and use additional tokens, which are shown in braces, e.g. {param1}.

#### 2.3.1 Virtual Registers

An unbounded number of *virtual registers* is a common abstraction in compilers [9]. Query compilers use them to handle attributes without the restrictions of machine registers. When replacing virtual registers with machine registers for execution, general purpose compilers perform live-range analysis [2]. This is rather expensive because compilers consider all execution-paths that lead to a register usage.

Query workloads use virtual registers in a much simpler way than general purpose code. They hold attribute data within a pipeline and the pipeline's execution path only consists of tight loops. This allows query compilers to use a simpler approach that skips live-range analysis. In Flounder IR, operator emitters mark the validity range of virtual registers. The **vreg** pseudo-instruction marks the start of a virtual register usage, e.g. by using

```

;start virtual register use

vreg {vreg_nameN}

```

and the clear pseudo-instruction marks the end of the usage, e.g. with

```

;finish virtual register use

clear {vreg_nameN} .

```

We use these markers in a way similar to scopes in higher-level languages. For instance the Flounder IR in Figure 2.4 (a) marks the range of the probe attributes {s\_a} and {s\_b} to reach around the operators that are contained in the probe loop.

#### 2.3.2 Function Calls

Being able to access pre-compiled functionality is important for query compilers. It reduces compile times and avoids the implementation cost of code generation for

every SQL feature. To this end Flounder IR provides the mcall pseudo-instructions to specify function calls in a simple way. For instance

```

;function call to ht_ins

mcall {res} {ht_ins} {param1} ... {paramN}

```

represents a function call to ht\_ins(...) with parameters param1 to paramN and the return value is stored in {res}. A pointer to the function code is provided as an address constant via {ht\_ins}. This pseudo-instruction is later replaced with an instruction sequence that realizes the calling convention.

#### 2.3.3 Constant Loads

Large constants, e.g. 64 bit, can not be used as *immediate operands* (imm) on current architectures. To use large constants, they have to be placed in machine registers. The *constant load* abstraction in Flounder IR, allows using such constants without restrictions. For instance the following instruction

```

; load from 64 bit address with offset mov {attr} [{0x7fff5a8e39d8} + {offs}]

```

loads data from the address {0x7fff5a8e39d8}+{offs} to the virtual register {attr}. During translation to machine assembly, the address constant will be placed in a machine register.

#### 2.3.4 Transparent High-Level Constructs

We use transparent high-level constructs that mimic high-level language features such as loops and conditional clauses. They are used to generate Flounder IR instructions in operator emitters. For example operator emitters can generate a while loop with the condition {tid} < {len} by using the methods While(...), close(...), and isSmaller(...) as shown below on the left.

```

loop_headN:

cmp {tid},{len}

jge loop_footN

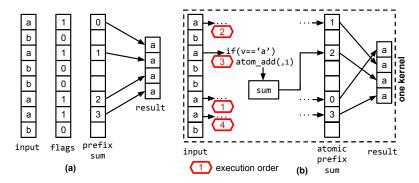

jge loop_footN

;loop body

[...]

} wl.close();

loop_headN:

jge loop_footN

;loop body

[...]

jmp loop_headN;

loop_footN:

;after loop

[...]

```

This generates the Flounder IR code shown on the right, that realizes the loop functionality. The start of the loop is marked with the label loop\_headN. The cmp instruction then evaluates the loop condition and jge jumps to the loop\_footN-label at the loop end, if the condition evaluates to false. Otherwise, the loop body is executed and after it, the loop starts over by executing the jump instruction jmp loop\_headN, which redirects control flow to the loop head.

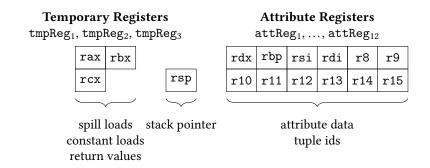

Figure 2.8: Usage of machine registers by the translator.

#### 2.4 Machine Code Translation

In the translation from Flounder IR to x86\_64 machine code, the abstractions that facilitated code generation in the previous step are now replaced with machine concepts. A key challenge here is to replace virtual registers with machine registers and to manage spill memory locations for cases of insufficient registers. Finding optimal register allocations is an NP-hard problem and even the computation of approximations is expensive [21]. In the context of JIT compilers, linear scan has been proposed as a faster algorithm [80] and was adopted by LLVM. However, linear scan register allocation is still relatively expensive due to live range computations and increasing numbers of registers.

The following presents a much simpler technique that benefits from the explicit usage ranges marked in Flounder IR. We first show the machine register configuration used by the translator and then show the algorithm for translation of the lightweight abstractions.

#### 2.4.1 Register Layout

We use a specific register layout for the machine code generated from Flounder IR. The layout is shown in Figure 2.8. We split the 16 integer registers of the  $x86\_64$  architecture into three categories.

We use twelve attribute registers  $\mathtt{attReg_1}$ , ...,  $\mathtt{attReg_{12}}$  to carry attribute data and tuple ids. We use three temporary registers  $\mathtt{tmpReg1}$ ,  $\mathtt{tmpReg2}$  and  $\mathtt{tmpReg3}$ , which are-multi purpose for accessing spill registers and constant loads. Lastly, we use the stack pointer  $\mathtt{rsp}$  to store the stack offset. The stack base pointer  $\mathtt{rbp}$  is repurposed for attribute data and not used for the stack.

#### 2.4.2 Translation Algorithm

The translation algorithm translates Flounder IR to x86\_64 assembly in one sequential pass over the code. It replaces the Flounder abstractions with machine

```

Translate Flounder IR to machine assembly

/* attribute registers in use */

2 foreach instruction i in input:

t \leftarrow 0

/* temporary registers in use */

3

/* allocate pseudo-instruction */

if i is vreg \{v\}:

4

if a < number attribute registers:

5

allocate free attReg_k

/* machine register */

a \leftarrow a + 1

/* spill */

8

else allocate spill location

elseif i is clear \{v\}: /* deallocate pseudo-instruction */

9

if any attReg<sub>k</sub> holds v:

10

release attReg_k

/* free machine reg */

11

a \leftarrow a - 1

12

elseif i is mcall (...): /* function call pseudo-instr.

13

emit call-convention code

14

/* other instructions */

15

foreach virtual register operand v in i:

16

if v is spilled:

17

/* spilled */

emit spill code for v to tmpReg<sub>t</sub>

18

replace v with tmpReg<sub>t</sub>

19

20

t \leftarrow t + 1

else replace v with attReg<sub>k</sub>

/* machine register */

21

foreach constant load operand c in i:

22

emit load c to tmpReg<sub>t</sub>

/* place c in temp reg */

23

replace c with tmpReg, in i

24

t \leftarrow t + 1

25

/* output native instruction */

emit i

26

```

Figure 2.9: Pseudocode for the translation of Flounder IR to machine assembly. The code is translated in one pass.

instructions, machine registers, and stack access. The algorithm is shown in Figure 2.9.

When iterating over the IR elements, the algorithm keeps track of a, the number of in-use attribute registers (line 1), and t, the number of temporary registers per instruction (line 3). We describe the translation in three parts. The first part is register allocation, then the replacement of virtual operands with machine operands in instructions, and finally function calls.

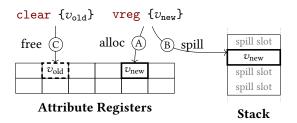

**Register Allocation** Register allocation is used to decide which virtual registers are stored in machine registers and which virtual registers are stored on the stack.

Register allocation does not produce code directly, but it sets the allocation state for spill code and operand replacement. The procedure is illustrated below.

When a **vreg**  $\{v_{\text{new}}\}$  pseudo-instruction is encountered (line 4), there are two options. In case A there are sufficient machine registers available and we assign one of them to  $v_{\text{new}}$  (lines 5-7). In case B all machine registers are occupied and we assign a spill slot on the stack (line 8). For **vreg**  $\{v_{\text{old}}\}$ , illustrated by C, any machine registers assigned to  $v_{\text{old}}$  are freed (line 11).

This assignment procedure has the effect that spilled virtual registers remain spilled. However, this happens only when the pipeline requires to hold more than 12 attributes simultaneously. As query compilers typically choose pipeline boundaries such that the data volume per tuple fits into the processor registers, this technique is a perfect match for query compilation.

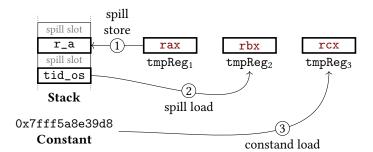

**Spill Code and Operand Replacement** For each instruction, operands that use *constant loads* or *virtual registers* have to be replaced with machine-compatible operands. Virtual registers that were assigned with machine registers are simply swapped (line 21). For the other cases, the algorithm uses tmpReg<sub>1</sub> to tmpReg<sub>3</sub> to hold values temporarily per instruction. Three registers are sufficient for this purpose as this is the highest numner of non-immediate operands per instruction. As an example, we look at the following instruction.

$$mov \{r_a\}, [\{0x7fff5a8e39d8\}+\{tid_os\}]$$

It reads an 8 byte value with the offset  $\{\text{tid_os}\}\$  from the memory address 0x7f... and stores it in  $\{r_a\}$ . The address is too large for an immediate operand and we assume for illustration purposes that both virtual registers  $\{r_a\}$  and  $\{\text{tid_os}\}$  are spilled.

The translator assigns temporary registers to each operand and emits *spill* code that exchanges values between spill slots and temporary registers. This is performed in pseudocode lines 16–26 and illustrated below.

The algorithm enumerates the virtual register accesses (lines 16-21) and the constant loads (lines 22-25) from the instruction. It assigns one of the temporary registers  $tmpReg_1$  to  $tmpReg_3$  to each. In step ① the translator assigns  $tmpReg_1$  (rax) to the operand  $\{r_a\}$ . This is the only output operand of the instruction and the operator emits a store to  $\{r_a\}$ 's spill slot on the stack. Step ② assigns  $tmpReg_2$  (rbx) to the operand  $\{tid_os\}$ . The translator emits a load to retrieve the value from its spill slot. Step ③ assigns  $tmpReg_3$  (rcx) to the constant load of address 0x7f... The translator emits a load for the constant. This results in the following machine code sequence, which includes the original mov instruction with replaced operands.

**Calling Conventions** During translation the mcall IR-instruction is replaced with a machine code sequence that performs the function call. To this end, a *calling convention* is applied, which specifies rules for the execution of function calls on a given hardware platform. It specifies the way registers are preserved across the call, how parameters are passed, and how the stack frame is adjusted. For the x86\_64 calling convention, the calling function preserves up to 7 integer registers (*caller-save registers*) and passes up to 6 parameters in integer registers before using the stack for parameter passing [61].

The call translation is initiated in line 14 of the Flounder IR translation algorithm (Figure 2.9). The machine register allocation to the point of the call is known. This allows us to generate a call sequence that is tailored to the current register usage.

The mcall translation algorithm is specified in Figure 2.10 and explained in the following. We use the call to ht\_get(..) from a previous example (Figure 2.4).

```

mcall {entry}, {ht_get}, {ht}, {r_a}, {entry}

```

It has the return value {entry}, the function address {ht\_get}, and the parameters {ht}, {r\_a} and {entry}. To derive the call-convention instruction sequence, the translator first replaces these operands with the already allocated machine operands (lines 1–3).

```

\label{eq:translate} \textbf{Translate} \; \textbf{mcall} \; \textbf{ret}, \, \textbf{func}, \, \textbf{p}_0, \, ..., \, \textbf{p}_n

1 foreach p in {ret, p_0,...,p_n}: /* replace virtual registers */

if p is virtual register: /* and use machine operands */

replace p with attribute register or stack location

4 R_{\text{caller-save}} = \{\text{rsi}, \text{rdi}, \text{r8}, \text{r9}, \text{r10}, \text{r11}\} /* A caller-save */

5 foreach register r in R_{\text{caller-save}}

if r is allocated:

/* check use */

emit save r to stack

s R_{param} = \{rdi, rsi, rdx, rcx, r8, r9\} /* B set parameters */

9 foreach parameter p_i in p_0, ..., p_n:

src \leftarrow p_i

10

/* handle overwrites */

if p_i was overwritten:

src \leftarrow stack backup of p_i

\mathbf{emit} \ \mathbf{mov} \ R_{\mathbf{param}_i}, \mathbf{src}

14 stackOffset ← total stack usage

/* C boilerplate call */

15 emit sub rsp, stackOffset

16 emit mov rax, func

17 emit call rax

18 emit add rsp, stackOffset

19 foreach register r in R_{\text{caller-save}}: /* D restore caller-save */

if r is allocated:

20

emit restore r from stack

22 emit mov ret, rax

/* get return value (C) */

```

Figure 2.10: Translate mcall IR-instruction to call-convention code.

```

mcall r11, 0x42fa10, 0x25cac0, r9, r11

```

Then the translator generates code that performs the following four steps:

- A Save caller-save registers that are in-use on the stack. These are r8, r9, r10 in the example (lines 4-6).

- B Assign parameter registers in the order specified by the ABI (lines 7-12). We assign 0x25cac0 to rdi, r9 to rsi, and r11 to rdx.

- C Place boiler-plate code to modify the stack frame, jump into the function, and to retrieve the return value (lines 13-17,21).

- D Restore caller-save registers (lines 18-20).

This results in the instruction sequence shown in Figure 2.11 that realizes the call in machine assembly. The instructions are annotated with **A** to **D** to indicate the step that generated them.

```

mov [rsp-8], r8

;A save caller-save

mov [rsp-16], r9

mov [rsp-24], r10

mov rdi, 0x25cac0

;B assign parameters

mov rsi, r9

mov rdx, r11

sub rsp, 24

;C boilerplate call

mov rax, 0x42fa10

call rax

add rsp, 24

mov r8, [rsp-8]

;D caller-save restore

mov r9, [rsp-16]

mov r10, [rsp-24]

mov r11, rax

;(C get return value)

```

Figure 2.11: Instruction sequence for the example function call.

#### 2.5 Getting More Out of Flounder

Flounder IR is a near-hardware representation for database processing functionality. This property enables additional uses and benefits for the IR. We present ideas on taking the IR's database specialization further by adding additional domain knowledge to the language. Then we show prefetching as an example of utilizing such domain knowledge. Finally, we discuss the use of Flounder IR as compilation vehicle for higher-level IRs.

#### 2.5.1 Utilizing Additional Database Knowledge

The domain specialization makes Flounder IR receptive to utilizing particular database knowledge. This idea can be extended in the way Flounder IR uses types. Currently it only uses machine datatypes. Alternatively, we can add SQL types to the IR. This simplifies the translation from SQL to Flounder because operator translators can directly emit instructions on SQL types. At the same time the responsibility of implementing SQL types and their special type characteristics moves down one level to the IR translation. This may open up interesting new ways for handling NULL-logic or types with multi-register representations (e.g. 128 bit decimals). The translator has the opportunity to apply simpler or unified logic to handle such characteristics.

Many database operators have optimized implementations that leverage hardware features, e.g. sort and hash-based operators [8]. Specifically applying vectorization techniques (e.g. AVX) has proven to be beneficial [98]. Flounder IR is a good match for such techniques because it gives explicit control over the instructions that are used. This helps to clearly express the way hardware optimizations are applied, which can be difficult with high-level languages that abstract hardware details. Similar to passing specific implementation aspects, additional hints about the database or about database statistics may be used. For instance information

2.6. EVALUATION 25

about relation and tuple sizes can be leveraged by the compiler for loop unrolling and prefetching. Hints about predicate selectivities are beneficial in estimating which branches are likely to be taken.

#### 2.5.2 Higher-Level IRs

Other IRs that describe data processing on a higher level than Flounder IR are frequently used. They are used as translation step for a specific query processing paradigm. For instance MonetDB uses MAL [14] for its column-style processing approach and SQLite uses a (high-level) bytecode representation for its bytecode interpreter [91]. Alternatively higher-level IRs can be used as an abstraction layer. As such they enable database systems to target different parallel hardware architectures [19, 79] or to handle multiple processing paradigms. The IR Voila [38], for instance, provides a representation that is suitable for compiled and interpreted execution. We take Voila's scatter operation as example to illustrate how Flounder can be leveraged for compiled execution of this IR. The scatter operation is used by hash-based operators to write values to the hash table. For example

```

// Voila scatter operation: Write key to HT

scatter ( ht.k1, new_pos |can_scatter, t[0] )

```

scatters the value t [0] to the hash table key location k1 of the bucket new\_pos. The scatter is executed conditionally depending on the flag can\_scatter. Translation to Flounder IR can implemented as a operator emitter, similar to Section 2.2.1. The Voila operation translates a short sequence of Flounder instructions:

```

;Scatter op in Flounder IR

cmp {can_scatter}, 0

je afterScatter

mov [{new_pos}+4], {t0}

afterScatter:

```

The cmp and je instructions evaluate {can\_scatter} to skip processing if necessary. Then mov performs the actual write of {t0} to the hash bucket with base address {new\_pos} and an exemplary offset +4.

#### 2.6 Evaluation

This section evaluates our approach of using a simple IR for query compilation that is specialized to relational workloads over using a general purpose IR. We use the micro prototype of a query compiler to evaluate the characteristics of different IR's along with their translation libraries. Then we use the ReSQL database system that was built on top of Flounder IR to evaluate the real world performance against other state-of-the-art systems.

**Micro Prototype** We use a smaller query compiler prototype that supports translation of query plans to *both* Flounder IR and LLVM IR. This allows us to evaluate the performance of both IRs on the same system. The prototype is used to execute the workloads from Figure 2.12. Flounder emits the binary representation of compiled queries with the AsmJit library [52] to avoid the overhead of running external assemblers, e.g. nasm. For LLVM IR, the machine code is generated by the LLVM library's JIT functionality. We use 00 and 03 optimization levels for tradeoffs between compilation time and code quality.

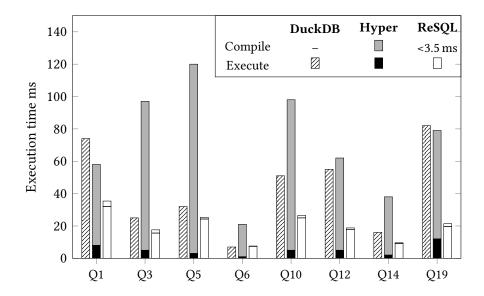

**Database Systems** We built the JIT-compiling database system ReSQL, which uses Flounder IR during compilation and has the ability to run various SQL queries. This allows us to evaluate the real world performance by executing TPC-H benchmark [13] queries. For comparison, we use one compilation-based system Hyper [69] and one interpretation-based system DuckDB [84]. We use Hyper version v0.5-222, which executes queries by JIT compiling via LLVM. We use DuckDB version v0.2.5, which executes queries with vector-at-a-time processing [16] for cache-efficiency. In its current development state, ReSQL only supports single-threaded execution. We configured all systems to run single-threaded for a fair comparison. Furthermore, ReSQL's query planner does not yet support sub-queries. Therefore we only use benchmark queries that do not contain sub-queries.

**Design of Characteristic Workloads** We use four query templates that allow us to evaluate different query characteristics. The templates are specified in Figure 2.12 in an SQL-form that uses additional integer parameters. The parameter l varies the data size in  $\mathbf{Q}_{\text{ol}}$ . Parameters p, j, and s vary query complexity in  $\mathbf{Q}_{\pi}$ ,  $\mathbf{Q}_{\bowtie}$ , and  $\mathbf{Q}_{\sigma}$  respectively. The attribute data is generated from uniform random distributions with the following relation sizes:  $\mathbf{Q}_{\text{ol}}$  has l tuples for r an s,  $\mathbf{Q}_{\pi}$  has 1 M tuples,  $\mathbf{Q}_{\bowtie}$  has 10 K tuples per join relation, and  $\mathbf{Q}_{\sigma}$  has 1 M tuples.

**Execution Platform** We use a system with Intel(R) Xeon E5-1607 v2 CPU with 3.00 GHz and 32 GB main memory. The experiments run in one thread. We use operating system Ubuntu 18.04.4 and clang++ 6.0.0 to compile the query compiler and the library for JIT queries. The LLVM backend uses LLVM 6.0.0.

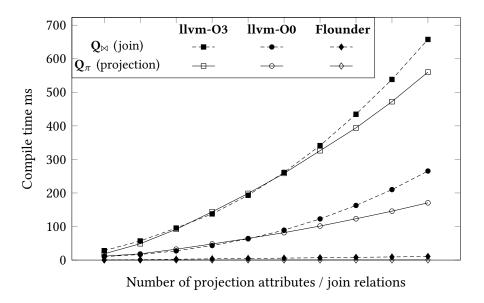

#### 2.6.1 Compilation Times

We compare the machine code compilation times for LLVM and Flounder for  $\mathbf{Q}_{\pi}$  and  $\mathbf{Q}_{\bowtie}$ . We use  $\mathbf{Q}_{\pi}$  with values of p to project 50 to an extreme case 500 attributes (filter with selectivity 1%). We use  $\mathbf{Q}_{\bowtie}$  with values of j to join 2 to 100 relations. We show the results for **Flounder**, **Ilvm-O0**, and **Ilvm-O3** in Figure 2.13.

**Observations** For all techniques, the compilation times increase with the query complexity. The compilation times for  $\mathbf{Q}_{\bowtie}$  are higher (up to 657 ms) than for  $\mathbf{Q}_{\pi}$  (up

2.6. EVALUATION 27

```

SELECT AVG(r.e)

SELECT r.a_1, r.a_2, ..., r.a_p

FROM r,s --len(r)=len(s)=l

FROM r

WHERE r.b = s.d

WHERE r.a_1 < c

AND r.c BETWEEN 40 AND 50

\mathbf{Q}_{0}: Vary relation lengths (l).

\mathbf{Q}_{\pi}: Vary projection complexity (p).

SELECT r.a

SELECT r_1.a, r_2.a, ..., r_j.a

FROM r

FROM r_1, r_2, ..., r_j

WHERE r.a != c_1

WHERE r_1.a = r_2.a

AND r.a != c_2

AND r_{i-1}.a = r_i.a

AND r.a != c_s

\mathbf{Q}_{\bowtie}: Vary join complexity (j).

\mathbf{Q}_{\sigma}: Vary selection complexity (s).

```

Figure 2.12: Query templates used to vary query characteristics.

Figure 2.13: Effect of query complexity on compilation times for different query compilation techniques.

to 560 ms) and we look in detail at  $\mathbf{Q}_{\bowtie}$ . With 00 optimization LLVM has compilation times between 10 ms up to 265 ms. With 03 compilation times range from 28 ms up to 657 ms. For both levels, the graphs show super-linear growth of compilation times with query complexity. **Flounder** shows lower compilation times that scale linearly between 0.3 ms to 10.8 ms. The highest factor of improvement is 24.6x over **llvm-O0**. and 60.9x over **llvm-O3** (both for 100 join relations). For  $\mathbf{Q}_{\pi}$  **Flounder** has very low compilations times ranging from 0.1 ms (50 attributes) to 0.6 ms (500 attributes). This leads to factors of improvement up to 933x over **llvm-O3**. We attribute this to the time LLVM spends on register allocation. This is due to the large number of virtual registers used to carry attributes for this workload.

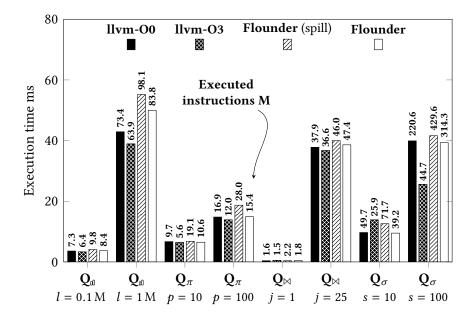

Figure 2.14: Time and instruction count for execution of machine code from different query compilation techniques.

#### 2.6.2 Machine Code Quality

To evaluate machine code quality, we execute two configurations of each query template and measure the *execution time* and the number of *executed instructions*. The results are shown in Figure 2.14. The bars show the execution time in milliseconds and the number on top shows the executed instructions in millions.

**Register Allocation** We analyze the effect of our register allocation strategy on machine code quality. To this end, we look at the techniques **Flounder** (spill) and **Flounder**. The former uses spill access for every virtual register use. The latter allocates machine registers with the translation algorithm. We observe that register allocation reduces the number of executed instructions by factors between  $1.2 \times$  and  $1.8 \times$  (with one exception). This shows that our register allocation strategy effectively reduces the amount of executed spill code. We explain the lack of improvement for  $\mathbb{Q}_{\bowtie}$  j=25 with a large number of hash table operations, which execute invariant library code. The results show that the register allocation technique reduces execution times for all queries by factors between  $1.02 \times$  to  $1.35 \times$ . The factors are not as high as the factors between L1 access and register access. This is because the memory access for reading relation data limits throughput (as is typical for database workloads). The improvements shown by the experiment are due to faster machine register access and execution of less spill code.

2.6. EVALUATION 29

Comparison with LLVM Next we compare the machine code quality of Flounder and LLVM (cf. Figure 2.14). On average **llvm-O0** executes 1.4× fewer instructions than **Flounder**. The execution times, however, are similar and are longer for **Flounder** only by an average factor of 1.01×. With regard to execution times, the machine code quality resulting from Flounder is similar to **llvm-O0**. We attribute the small time difference despite the higher instruction count to memory bound execution.

The technique **llvm-O3** executes  $2.2\times$  fewer instructions than **Flounder** on average. The average factor between the execution times of  $1.05\times$  is still low. However, especially queries on larger datasets benefit from the optimizations applied by **llvm-O3**. E.g. the larger variant  $\mathbf{Q}_{\square}$  1 M executes  $1.3\times$  faster. We conclude that despite the much shorter translation times, our compilation strategy produces code with competitive performance to the machine code generated by LLVM.

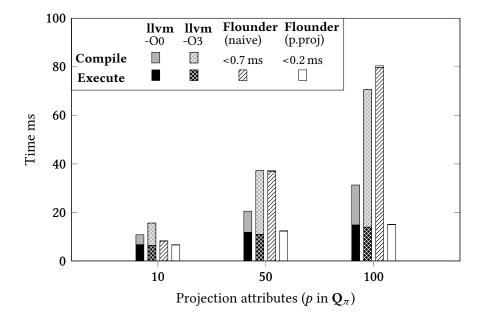

### 2.6.3 Post-Projection Optimizations

The workload  $\mathbf{Q}_{\pi}$  benefits from post-projection optimizations. For increasing numbers of projection attributes p, it is preferable to read attributes  $\mathbf{a}_2$  to  $\mathbf{a}_p$  only for tuples that pass the filter (1% of the relation) instead of performing a full scan. We analyze how the code generation strategies handle post-projection optimization by executing  $\mathbf{Q}_{\pi}$  with  $p = \{10, 50, 100\}$ . We use the llvm-based techniques, **Flounder** (naive), and **Flounder** (p.proj). The technique **Flounder** (p.proj) produces IR with explicit post-projection; the other techniques produce IR with full scans.

**Observations** The experiment results are shown in Figure 2.15. We observe that **Flounder** (naive) has execution times between 8.2 ms and 79.7 ms, and **Flounder** (p.proj) has lower execution times between 6.6 ms and 15.0 ms. Adding post-projection reduces execution times by factors up to 5.3x. The LLVM-based techniques have execution times between 6.4 ms and 14.8 ms. Despite not using post-projection explicitly, LLVM has similar execution performance as the post-projection strategy. We explain this by LLVM adding a similar optimization during machine code generation.

However, these optimization capabilities of LLVM come at the cost of high compilation times (up to 56.7 ms compared to 0.2 ms for **Flounder**). Although **Flounder** does not apply post-projection optimizations automatically, explicit control over post-projections is preferable for DBMSs, which typically use decision mechanisms for projection strategies.

### 2.6.4 Overall Performance for Characteristic Workloads

We show a table with the overall performance for each technique in Figure 2.16. The workloads are the same as in Section 2.6.2 with two configurations for each

Figure 2.15: Processing the projection workload varying compilation and projection techniques.

|                                             | llvm-O0 |      |       | llvm-O3 |      |       | Flounder |      |             |

|---------------------------------------------|---------|------|-------|---------|------|-------|----------|------|-------------|